Intel(R) IQ80315 I/O Processor DMA and XOR Library APIs and ...

Intel(R) IQ80315 I/O Processor DMA and XOR Library APIs and ...

Intel(R) IQ80315 I/O Processor DMA and XOR Library APIs and ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

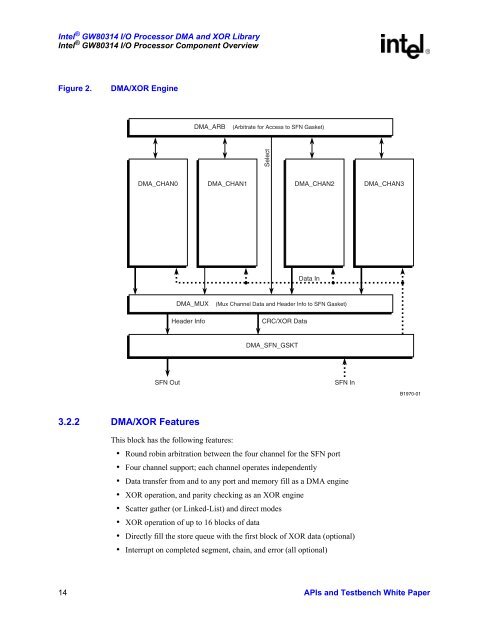

<strong>Intel</strong> ® GW80314 I/O <strong>Processor</strong> <strong>DMA</strong> <strong>and</strong> <strong>XOR</strong> <strong>Library</strong><strong>Intel</strong> ® GW80314 I/O <strong>Processor</strong> Component OverviewFigure 2.<strong>DMA</strong>/<strong>XOR</strong> Engine<strong>DMA</strong>_ARB(Arbitrate for Access to SFN Gasket)Select<strong>DMA</strong>_CHAN0<strong>DMA</strong>_CHAN1 <strong>DMA</strong>_CHAN2 <strong>DMA</strong>_CHAN3Data In<strong>DMA</strong>_MUXHeader Info(Mux Channel Data <strong>and</strong> Header Info to SFN Gasket)CRC/<strong>XOR</strong> Data<strong>DMA</strong>_SFN_GSKTSFN OutSFN InB1970-013.2.2 <strong>DMA</strong>/<strong>XOR</strong> FeaturesThis block has the following features:• Round robin arbitration between the four channel for the SFN port• Four channel support; each channel operates independently• Data transfer from <strong>and</strong> to any port <strong>and</strong> memory fill as a <strong>DMA</strong> engine• <strong>XOR</strong> operation, <strong>and</strong> parity checking as an <strong>XOR</strong> engine• Scatter gather (or Linked-List) <strong>and</strong> direct modes• <strong>XOR</strong> operation of up to 16 blocks of data• Directly fill the store queue with the first block of <strong>XOR</strong> data (optional)• Interrupt on completed segment, chain, <strong>and</strong> error (all optional)14 <strong>APIs</strong> <strong>and</strong> Testbench White Paper