Intel(R) IQ80315 I/O Processor DMA and XOR Library APIs and ...

Intel(R) IQ80315 I/O Processor DMA and XOR Library APIs and ...

Intel(R) IQ80315 I/O Processor DMA and XOR Library APIs and ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

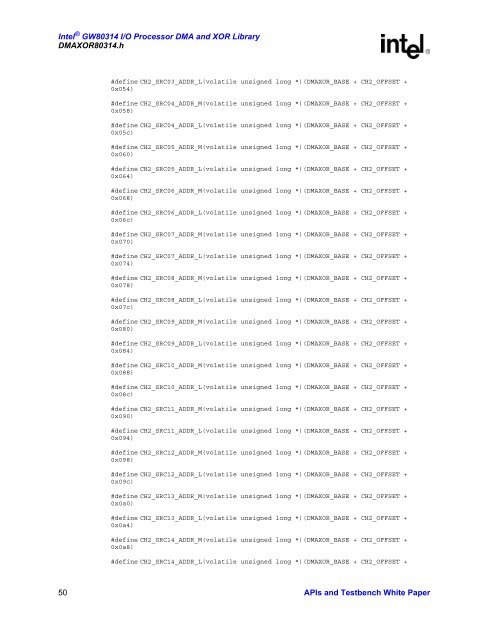

<strong>Intel</strong> ® GW80314 I/O <strong>Processor</strong> <strong>DMA</strong> <strong>and</strong> <strong>XOR</strong> <strong>Library</strong><strong>DMA</strong><strong>XOR</strong>80314.h#define CH2_SRC03_ADDR_L(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x054)#define CH2_SRC04_ADDR_M(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x058)#define CH2_SRC04_ADDR_L(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x05c)#define CH2_SRC05_ADDR_M(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x060)#define CH2_SRC05_ADDR_L(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x064)#define CH2_SRC06_ADDR_M(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x068)#define CH2_SRC06_ADDR_L(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x06c)#define CH2_SRC07_ADDR_M(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x070)#define CH2_SRC07_ADDR_L(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x074)#define CH2_SRC08_ADDR_M(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x078)#define CH2_SRC08_ADDR_L(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x07c)#define CH2_SRC09_ADDR_M(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x080)#define CH2_SRC09_ADDR_L(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x084)#define CH2_SRC10_ADDR_M(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x088)#define CH2_SRC10_ADDR_L(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x08c)#define CH2_SRC11_ADDR_M(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x090)#define CH2_SRC11_ADDR_L(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x094)#define CH2_SRC12_ADDR_M(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x098)#define CH2_SRC12_ADDR_L(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x09c)#define CH2_SRC13_ADDR_M(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x0a0)#define CH2_SRC13_ADDR_L(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x0a4)#define CH2_SRC14_ADDR_M(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +0x0a8)#define CH2_SRC14_ADDR_L(volatile unsigned long *)(<strong>DMA</strong><strong>XOR</strong>_BASE + CH2_OFFSET +50 <strong>APIs</strong> <strong>and</strong> Testbench White Paper