Workshopband als PDF - Mpc.belwue.de

Workshopband als PDF - Mpc.belwue.de

Workshopband als PDF - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

MPC-WORKSHOP FEBRUAR 2013<br />

Optimierung eines 32-Bit-Softcores mit<br />

Harvard-Architektur und Dual Cache sowie<br />

Memory Management Unit für Embed<strong>de</strong>d Computing<br />

Michael Schmidt, Sebastian Stickel, Florian Zowislok, Dirk Jansen<br />

Zusammenfassung—Die SIRIUS-Prozessorfamilie<br />

ist eine am Institut für Angewandte Forschung <strong>de</strong>r<br />

Hochschule Offenburg entwickelte Prozessorreihe,<br />

welche ursprünglich zu Lehrzwecken entwickelt<br />

wur<strong>de</strong>. Sie umfasst zwischenzeitlich drei Softcores,<br />

die sich alle in Performance, Funktionalität und<br />

damit einhergehend auch in Komplexität unterschei<strong>de</strong>n.<br />

Der Schwerpunkt dieser Veröffentlichung<br />

liegt auf <strong>de</strong>r leistungsstärksten Variante <strong>de</strong>r<br />

drei Softcores, <strong>de</strong>m SIRIUS HULK. Insbeson<strong>de</strong>re<br />

die vorgenommen Optimierungen an Hardware<br />

und Software sowie die Syntheseergebnisse wer<strong>de</strong>n<br />

vorgestellt und erläutert.<br />

Schlüsselwörter—SIRIUS, Prozessorkern, Prozessor,<br />

Softcore, Harvard Architektur, FPGA,<br />

Benchmarking, Synthese.<br />

I. EINLEITUNG<br />

Als Teil <strong>de</strong>s Instituts für angewandte Forschung<br />

(IAF) entwickelt das ASIC Design Center <strong>de</strong>r Hochschule<br />

Offenburg seit 1989 anwen<strong>de</strong>rspezifische<br />

Schaltungen (ASICs). Ferner wur<strong>de</strong> vor einigen Jahren<br />

mit <strong>de</strong>r Entwicklung eines hauseigenen Prozessorkerns<br />

namens SIRIUS für Forschung und Lehre <strong>de</strong>r<br />

Stu<strong>de</strong>nten begonnen. Dieser verfügte seinerzeit über<br />

eine Von-Neumann-Architektur, einen 16 Bit breiten<br />

Datenbus sowie über einen beschränkten RISC-<br />

Befehlssatz und konnte sämtliche Register-Register<br />

Befehle in einem Taktzyklus abarbeiten. Darüber<br />

hinaus verfügte er über zwei Betriebsmodi, <strong>de</strong>n 16-<br />

und <strong>de</strong>n 32-Bit-Modus, die es ihm ermöglichten, optimal<br />

auf <strong>de</strong>n Zieleinsatz abgestimmt zu wer<strong>de</strong>n. Diese<br />

Prozessorkernphilosophie wur<strong>de</strong> <strong>als</strong> Grundlage für<br />

eine ganze Prozessorfamilie verwen<strong>de</strong>t, die nun unter<br />

<strong>de</strong>m Familiennamen SIRIUS weiterentwickelt wird.<br />

Der bisherige SIRIUS-Kern wur<strong>de</strong> in SIRIUS Janus<br />

umbenannt und kommt beispielsweise im hauseigenen<br />

PDA in UMC 0.18 µm Technologie zum Einsatz. Als<br />

kompaktesten Vertreter gibt es <strong>de</strong>n SIRIUS Tiny, <strong>de</strong>r<br />

über eine v. Neumann-Architektur und einen 16 Bit<br />

breiten Datenbus verfügt.<br />

Michael Schmidt, michael.schmidt@hs-offenburg.<strong>de</strong>, Sebastian<br />

Stickel, sebastian.stickel@hs-offenburg.<strong>de</strong>, Florian Zowislok (Ehemaliger<br />

Mitarbeiter), Dirk Jansen, d.jansen@hs-offenburg.<strong>de</strong>,<br />

Hochschule für Technik, Wirtschaft und Medien – Offenburg,<br />

University of Applied Sciences, Badstraße 24, 77652 Offenburg.<br />

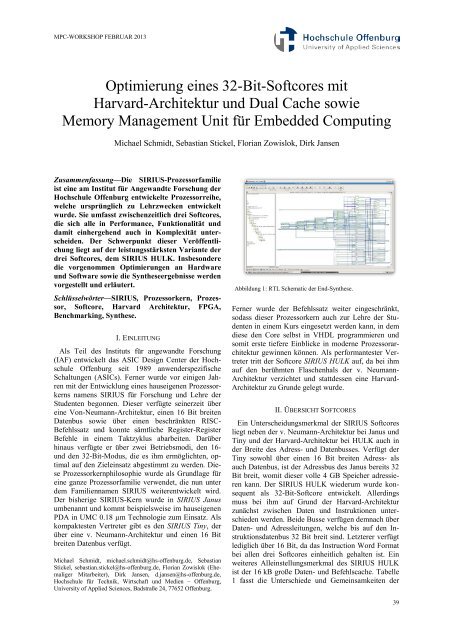

Abbildung 1: RTL Schematic <strong>de</strong>r End-Synthese.<br />

Ferner wur<strong>de</strong> <strong>de</strong>r Befehlssatz weiter eingeschränkt,<br />

sodass dieser Prozessorkern auch zur Lehre <strong>de</strong>r Stu<strong>de</strong>nten<br />

in einem Kurs eingesetzt wer<strong>de</strong>n kann, in <strong>de</strong>m<br />

diese <strong>de</strong>n Core selbst in VHDL programmieren und<br />

somit erste tiefere Einblicke in mo<strong>de</strong>rne Prozessorarchitektur<br />

gewinnen können. Als performantester Vertreter<br />

tritt <strong>de</strong>r Softcore SIRIUS HULK auf, da bei ihm<br />

auf <strong>de</strong>n berühmten Flaschenh<strong>als</strong> <strong>de</strong>r v. Neumann-<br />

Architektur verzichtet und statt<strong>de</strong>ssen eine Harvard-<br />

Architektur zu Grun<strong>de</strong> gelegt wur<strong>de</strong>.<br />

II. ÜBERSICHT SOFTCORES<br />

Ein Unterscheidungsmerkmal <strong>de</strong>r SIRIUS Softcores<br />

liegt neben <strong>de</strong>r v. Neumann-Architektur bei Janus und<br />

Tiny und <strong>de</strong>r Harvard-Architektur bei HULK auch in<br />

<strong>de</strong>r Breite <strong>de</strong>s Adress- und Datenbusses. Verfügt <strong>de</strong>r<br />

Tiny sowohl über einen 16 Bit breiten Adress- <strong>als</strong><br />

auch Datenbus, ist <strong>de</strong>r Adressbus <strong>de</strong>s Janus bereits 32<br />

Bit breit, womit dieser volle 4 GB Speicher adressieren<br />

kann. Der SIRIUS HULK wie<strong>de</strong>rum wur<strong>de</strong> konsequent<br />

<strong>als</strong> 32-Bit-Softcore entwickelt. Allerdings<br />

muss bei ihm auf Grund <strong>de</strong>r Harvard-Architektur<br />

zunächst zwischen Daten und Instruktionen unterschie<strong>de</strong>n<br />

wer<strong>de</strong>n. Bei<strong>de</strong> Busse verfügen <strong>de</strong>mnach über<br />

Daten- und Adressleitungen, welche bis auf <strong>de</strong>n Instruktionsdatenbus<br />

32 Bit breit sind. Letzterer verfügt<br />

lediglich über 16 Bit, da das Instruction Word Format<br />

bei allen drei Softcores einheitlich gehalten ist. Ein<br />

weiteres Alleinstellungsmerkmal <strong>de</strong>s SIRIUS HULK<br />

ist <strong>de</strong>r 16 kB große Daten- und Befehlscache. Tabelle<br />

1 fasst die Unterschie<strong>de</strong> und Gemeinsamkeiten <strong>de</strong>r<br />

39

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)