High Performance Microchip Supply - Under Secretary of Defense ...

High Performance Microchip Supply - Under Secretary of Defense ...

High Performance Microchip Supply - Under Secretary of Defense ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

_________________________________________________________________ APPENDIX G<br />

APPENDIX G. COMPARISON OF ASIC AND FPGA SYSTEM<br />

CHARACTERISTICS<br />

Power Dissipation<br />

Utilization <strong>of</strong> Available Transistors<br />

Signal Processing <strong>Performance</strong><br />

Typical Hardware Fabrication Time<br />

Fabrication Cost<br />

Physical Size<br />

Available Sizes<br />

Ability To Upgrade After Put Into Use<br />

Ability To Isolate “Red”/“Black” Regions<br />

Flexibility Of I/O Protocols<br />

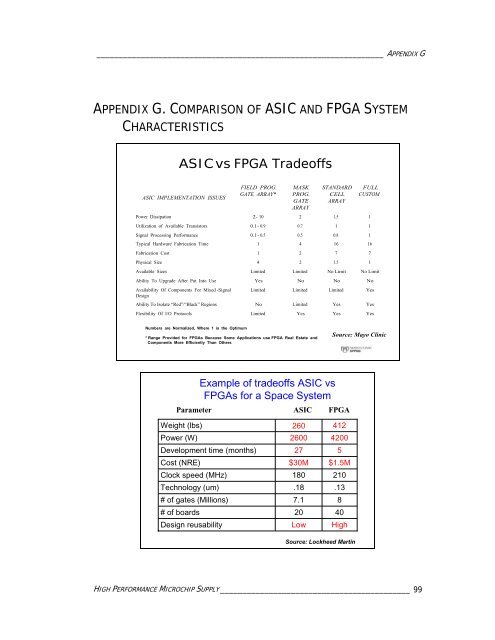

ASIC vs FPGA Trade<strong>of</strong>fs<br />

ASIC IMPLEMENTATION ISSUES<br />

Availability Of Components For Mixed -Signal<br />

Design<br />

Numbers are Normalized, Where 1 is the Optimum<br />

FIELD PROG.<br />

GATE ARRAY*<br />

2 - 10<br />

0.1 - 0.9<br />

0.1 - 0.5<br />

1<br />

1<br />

4<br />

Limited<br />

Yes<br />

Limited<br />

No<br />

Limited<br />

MASK<br />

PROG.<br />

GATE<br />

ARRAY<br />

HIGH PERFORMANCE MICROCHIP SUPPLY ___________________________________________<br />

99<br />

2<br />

4<br />

2<br />

2<br />

Limited<br />

No<br />

Limited<br />

Limited<br />

* Range Provided for FPGAs Because Some Applications use FPGA Real Estate and<br />

Components More Efficiently Than Others<br />

Yes<br />

Example <strong>of</strong> trade<strong>of</strong>fs ASIC vs<br />

FPGAs for a Space System<br />

0.7<br />

0.5<br />

STANDARD<br />

CELL<br />

ARRAY<br />

1.5<br />

1<br />

0.8<br />

16<br />

7<br />

1.5<br />

No Limit<br />

No<br />

Limited<br />

Parameter ASIC FPGA<br />

Weight (lbs)<br />

Power (W)<br />

Development time (months)<br />

Cost (NRE)<br />

Clock speed (MHz)<br />

Technology (um)<br />

# <strong>of</strong> gates (Millions)<br />

# <strong>of</strong> boards<br />

Design reusability<br />

260<br />

2600<br />

27<br />

$30M<br />

180<br />

.18<br />

7.1<br />

20<br />

Low<br />

Yes<br />

Yes<br />

FULL<br />

CUSTOM<br />

1<br />

1<br />

1<br />

16<br />

7<br />

1<br />

No Limit<br />

No<br />

Yes<br />

Yes<br />

Yes<br />

Source: Mayo Clinic<br />

412<br />

4200<br />

5<br />

$1.5M<br />

210<br />

.13<br />

8<br />

40<br />

<strong>High</strong><br />

Source: Lockheed Martin