Full-Custom Layout of an SRAM-Based FPGA - University of Toronto

Full-Custom Layout of an SRAM-Based FPGA - University of Toronto

Full-Custom Layout of an SRAM-Based FPGA - University of Toronto

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

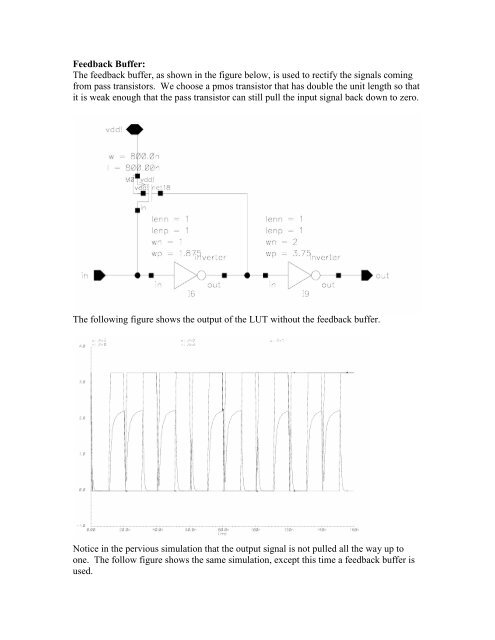

Feedback Buffer:<br />

The feedback buffer, as shown in the figure below, is used to rectify the signals coming<br />

from pass tr<strong>an</strong>sistors. We choose a pmos tr<strong>an</strong>sistor that has double the unit length so that<br />

it is weak enough that the pass tr<strong>an</strong>sistor c<strong>an</strong> still pull the input signal back down to zero.<br />

The following figure shows the output <strong>of</strong> the LUT without the feedback buffer.<br />

Notice in the pervious simulation that the output signal is not pulled all the way up to<br />

one. The follow figure shows the same simulation, except this time a feedback buffer is<br />

used.