Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

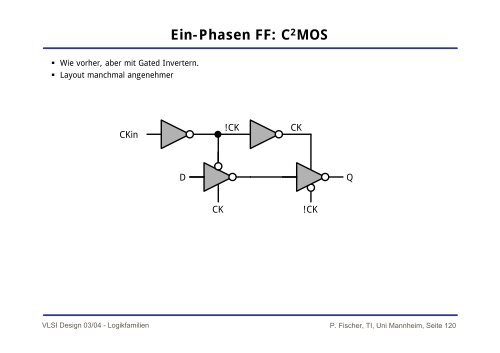

� Wie vorher, aber mit Gated Invertern.<br />

� Layout manchmal angenehmer<br />

CKin<br />

VLSI Design 03/04 - <strong>Logikfamilien</strong><br />

Ein-Phasen FF: C 2 MOS<br />

D<br />

CK<br />

!CK<br />

CK<br />

!CK<br />

Q<br />

P. Fischer, TI, Uni Mannheim, Seite 120