Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

VLSI Design 03/04 - <strong>Logikfamilien</strong><br />

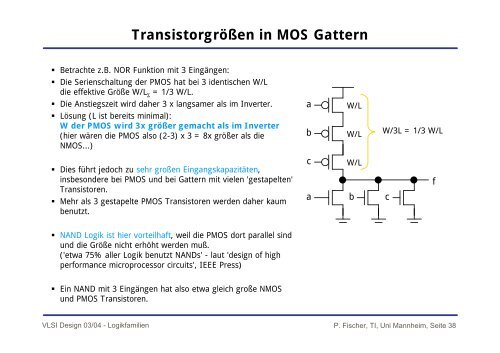

Transistorgrößen in MOS Gattern<br />

� Betrachte z.B. NOR Funktion mit 3 Eingängen:<br />

� Die Serienschaltung der PMOS hat bei 3 identischen W/L<br />

die effektive Größe W/L Σ = 1/3 W/L.<br />

� Die Anstiegszeit wird daher 3 x langsamer als im Inverter.<br />

� Lösung (L ist bereits minimal):<br />

W der PMOS wird 3x größer gemacht als im Inverter<br />

(hier wären die PMOS also (2-3) x 3 = 8x größer als die<br />

NMOS...)<br />

� Dies führt jedoch zu sehr großen Eingangskapazitäten,<br />

insbesondere bei PMOS und bei Gattern mit vielen 'gestapelten'<br />

Transistoren.<br />

� Mehr als 3 gestapelte PMOS Transistoren werden daher kaum<br />

benutzt.<br />

� NAND Logik ist hier vorteilhaft, weil die PMOS dort parallel sind<br />

und die Größe nicht erhöht werden muß.<br />

('etwa 75% aller Logik benutzt NANDs' - laut 'design of high<br />

performance microprocessor circuits', IEEE Press)<br />

� Ein NAND mit 3 Eingängen hat also etwa gleich große NMOS<br />

und PMOS Transistoren.<br />

a<br />

b<br />

c<br />

a<br />

W/L<br />

W/L<br />

W/L<br />

b c<br />

W/3L = 1/3 W/L<br />

P. Fischer, TI, Uni Mannheim, Seite 38<br />

f