Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

VLSI Design 03/04 - <strong>Logikfamilien</strong><br />

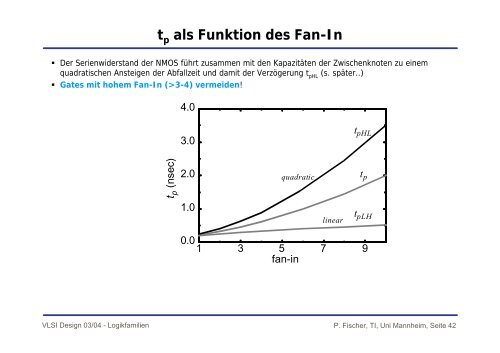

t p als Funktion des Fan-In<br />

� Der Serienwiderstand der NMOS führt zusammen mit den Kapazitäten der Zwischenknoten zu einem<br />

quadratischen Ansteigen der Abfallzeit und damit der Verzögerung t pHL (s. später..)<br />

� Gates mit hohem Fan-In (>3-4) vermeiden!<br />

t p (nsec)<br />

4.0<br />

3.0<br />

2.0<br />

1.0<br />

quadratic<br />

linear<br />

t pHL<br />

0.0<br />

1 3 5<br />

fan-in<br />

7 9<br />

t p<br />

t pLH<br />

AVOID LARGE FAN-IN GATES! (Typically not more than FI < 4)<br />

P. Fischer, TI, Uni Mannheim, Seite 42