Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

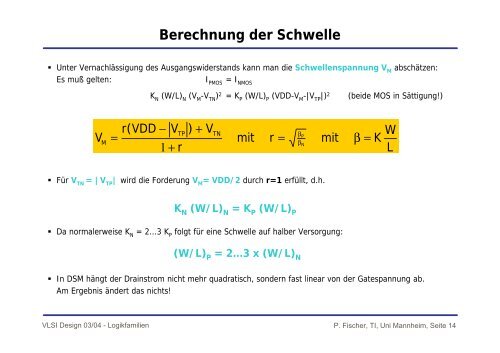

� Unter Vernachlässigung des Ausgangswiderstands kann man die Schwellenspannung V M abschätzen:<br />

Es muß gelten: I PMOS = I NMOS<br />

r(<br />

VDD −<br />

VLSI Design 03/04 - <strong>Logikfamilien</strong><br />

K N (W/L) N (V M -V TN ) 2 = K P (W/L) P (VDD-V M -|V TP |) 2 (beide MOS in Sättigung!)<br />

� Für V TN = |V TP | wird die Forderung V M = VDD/2 durch r=1 erfüllt, d.h.<br />

K N (W/L) N = K P (W/L) P<br />

� Da normalerweise K N = 2...3 K P folgt für eine Schwelle auf halber Versorgung:<br />

(W/L) P = 2...3 x (W/L) N<br />

� In DSM hängt der Drainstrom nicht mehr quadratisch, sondern fast linear von der Gatespannung ab.<br />

Am Ergebnis ändert das nichts!<br />

Berechnung der Schwelle<br />

V<br />

1<br />

+ r<br />

)<br />

+<br />

V<br />

mit<br />

TP TN<br />

βP<br />

VM = = βN<br />

r<br />

mit<br />

β<br />

=<br />

K<br />

W<br />

L<br />

P. Fischer, TI, Uni Mannheim, Seite 14