Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

VLSI Design 03/04 - <strong>Logikfamilien</strong><br />

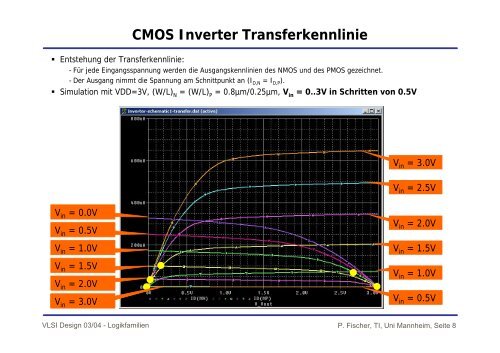

<strong>CMOS</strong> Inverter Transferkennlinie<br />

� Entstehung der Transferkennlinie:<br />

- Für jede Eingangsspannung werden die Ausgangskennlinien des NMOS und des PMOS gezeichnet.<br />

- Der Ausgang nimmt die Spannung am Schnittpunkt an (I D,N = I D,P ).<br />

� Simulation mit VDD=3V, (W/L) N = (W/L) P = 0.8µm/0.25µm, V in = 0..3V in Schritten von 0.5V<br />

V in = 0.0V<br />

V in = 0.5V<br />

V in = 1.0V<br />

V in = 1.5V<br />

V in = 2.0V<br />

V in = 3.0V<br />

2.5V<br />

V in = 3.0V<br />

V in = 2.5V<br />

V in = 2.0V<br />

V in = 1.5V<br />

V in = 1.0V<br />

V in = 0.0V 0.5V<br />

P. Fischer, TI, Uni Mannheim, Seite 8