Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Logikfamilien: CMOS, dynamisch,... (7.3Mb)

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

VLSI Design 03/04 - <strong>Logikfamilien</strong><br />

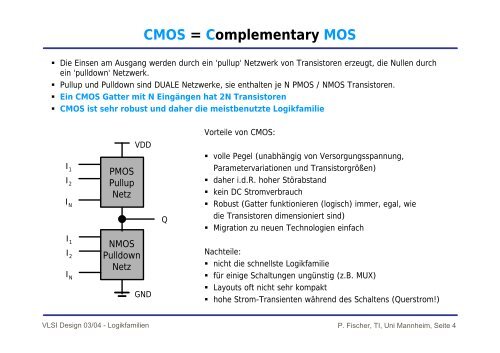

<strong>CMOS</strong> = Complementary MOS<br />

� Die Einsen am Ausgang werden durch ein 'pullup' Netzwerk von Transistoren erzeugt, die Nullen durch<br />

ein 'pulldown' Netzwerk.<br />

� Pullup und Pulldown sind DUALE Netzwerke, sie enthalten je N PMOS / NMOS Transistoren.<br />

� Ein <strong>CMOS</strong> Gatter mit N Eingängen hat 2N Transistoren<br />

� <strong>CMOS</strong> ist sehr robust und daher die meistbenutzte Logikfamilie<br />

I 1<br />

I 2<br />

I N<br />

I 1<br />

I 2<br />

I N<br />

PMOS<br />

Pullup<br />

Netz<br />

NMOS<br />

Pulldown<br />

Netz<br />

VDD<br />

GND<br />

Q<br />

Vorteile von <strong>CMOS</strong>:<br />

� volle Pegel (unabhängig von Versorgungsspannung,<br />

Parametervariationen und Transistorgrößen)<br />

� daher i.d.R. hoher Störabstand<br />

� kein DC Stromverbrauch<br />

� Robust (Gatter funktionieren (logisch) immer, egal, wie<br />

die Transistoren dimensioniert sind)<br />

� Migration zu neuen Technologien einfach<br />

Nachteile:<br />

� nicht die schnellste Logikfamilie<br />

� für einige Schaltungen ungünstig (z.B. MUX)<br />

� Layouts oft nicht sehr kompakt<br />

� hohe Strom-Transienten während des Schaltens (Querstrom!)<br />

P. Fischer, TI, Uni Mannheim, Seite 4