Configuration and Remote System Upgrades in Cyclone IV ... - Altera

Configuration and Remote System Upgrades in Cyclone IV ... - Altera

Configuration and Remote System Upgrades in Cyclone IV ... - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

8–30 Chapter 8: <strong>Configuration</strong> <strong>and</strong> <strong>Remote</strong> <strong>System</strong> <strong>Upgrades</strong> <strong>in</strong> <strong>Cyclone</strong> <strong>IV</strong> Devices<br />

<strong>Configuration</strong><br />

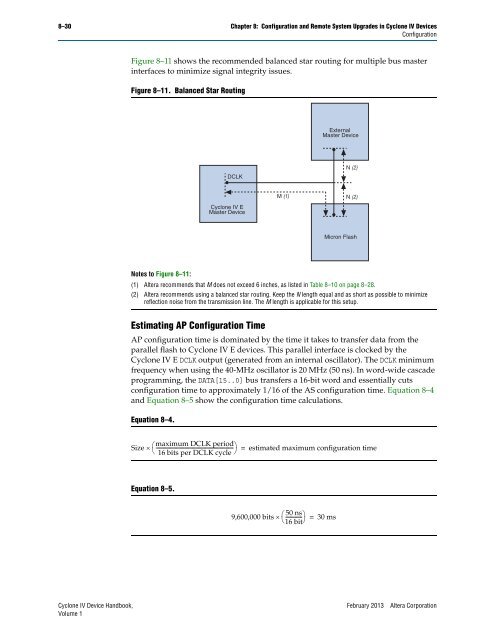

Figure 8–11 shows the recommended balanced star rout<strong>in</strong>g for multiple bus master<br />

<strong>in</strong>terfaces to m<strong>in</strong>imize signal <strong>in</strong>tegrity issues.<br />

Figure 8–11. Balanced Star Rout<strong>in</strong>g<br />

Notes to Figure 8–11:<br />

(1) <strong>Altera</strong> recommends that M does not exceed 6 <strong>in</strong>ches, as listed <strong>in</strong> Table 8–10 on page 8–28.<br />

(2) <strong>Altera</strong> recommends us<strong>in</strong>g a balanced star rout<strong>in</strong>g. Keep the N length equal <strong>and</strong> as short as possible to m<strong>in</strong>imize<br />

reflection noise from the transmission l<strong>in</strong>e. The M length is applicable for this setup.<br />

Estimat<strong>in</strong>g AP <strong>Configuration</strong> Time<br />

AP configuration time is dom<strong>in</strong>ated by the time it takes to transfer data from the<br />

parallel flash to <strong>Cyclone</strong> <strong>IV</strong> E devices. This parallel <strong>in</strong>terface is clocked by the<br />

<strong>Cyclone</strong> <strong>IV</strong> E DCLK output (generated from an <strong>in</strong>ternal oscillator). The DCLK m<strong>in</strong>imum<br />

frequency when us<strong>in</strong>g the 40-MHz oscillator is 20 MHz (50 ns). In word-wide cascade<br />

programm<strong>in</strong>g, the DATA[15..0] bus transfers a 16-bit word <strong>and</strong> essentially cuts<br />

configuration time to approximately 1/16 of the AS configuration time. Equation 8–4<br />

<strong>and</strong> Equation 8–5 show the configuration time calculations.<br />

Equation 8–4.<br />

Equation 8–5.<br />

DCLK<br />

<strong>Cyclone</strong> <strong>IV</strong> E<br />

Master Device<br />

External<br />

Master Device<br />

Micron Flash<br />

maximum DCLK period<br />

Size ---------------------------------------------------------------- <br />

16 bits per DCLK cycle <br />

= estimated maximum configuration time<br />

<strong>Cyclone</strong> <strong>IV</strong> Device H<strong>and</strong>book, February 2013 <strong>Altera</strong> Corporation<br />

Volume 1<br />

M (1)<br />

50 ns<br />

9,600,000 bits ------------- =<br />

30 ms<br />

16 bit<br />

N (2)<br />

N (2)