Configuration and Remote System Upgrades in Cyclone IV ... - Altera

Configuration and Remote System Upgrades in Cyclone IV ... - Altera

Configuration and Remote System Upgrades in Cyclone IV ... - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 8: <strong>Configuration</strong> <strong>and</strong> <strong>Remote</strong> <strong>System</strong> <strong>Upgrades</strong> <strong>in</strong> <strong>Cyclone</strong> <strong>IV</strong> Devices 8–49<br />

<strong>Configuration</strong><br />

You can perform JTAG test<strong>in</strong>g on <strong>Cyclone</strong> <strong>IV</strong> devices before, dur<strong>in</strong>g, <strong>and</strong> after<br />

configuration. <strong>Cyclone</strong> <strong>IV</strong> devices support the BYPASS, IDCODE, <strong>and</strong> SAMPLE<br />

<strong>in</strong>structions dur<strong>in</strong>g configuration without <strong>in</strong>terrupt<strong>in</strong>g configuration. All other JTAG<br />

<strong>in</strong>structions can only be issued by first <strong>in</strong>terrupt<strong>in</strong>g configuration <strong>and</strong><br />

reprogramm<strong>in</strong>g I/O p<strong>in</strong>s with the ACT<strong>IV</strong>E_DISENGAGE <strong>and</strong> CONFIG_IO <strong>in</strong>structions.<br />

The CONFIG_IO <strong>in</strong>struction allows you to configure the I/O buffers through the JTAG<br />

port <strong>and</strong> <strong>in</strong>terrupts configuration when issued after the ACT<strong>IV</strong>E_DISENGAGE<br />

<strong>in</strong>struction. This <strong>in</strong>struction allows you to perform board-level test<strong>in</strong>g prior to<br />

configur<strong>in</strong>g the <strong>Cyclone</strong> <strong>IV</strong> device or wait<strong>in</strong>g for a configuration device to complete<br />

configuration. Prior to issu<strong>in</strong>g the CONFIG_IO <strong>in</strong>struction, you must issue the<br />

ACT<strong>IV</strong>E_DISENGAGE <strong>in</strong>struction. This is because <strong>in</strong> <strong>Cyclone</strong> <strong>IV</strong> devices, the CONFIG_IO<br />

<strong>in</strong>struction does not hold nSTATUS low until reconfiguration, so you must disengage<br />

the active configuration mode controller when active configuration is <strong>in</strong>terrupted.<br />

The ACT<strong>IV</strong>E_DISENGAGE <strong>in</strong>struction places the active configuration mode controllers <strong>in</strong><br />

an idle state prior to JTAG programm<strong>in</strong>g. Additionally, the ACT<strong>IV</strong>E_ENGAGE <strong>in</strong>struction<br />

allows you to re-engage a disengaged active configuration mode controller.<br />

1 You must follow a specific flow when execut<strong>in</strong>g the ACT<strong>IV</strong>E_DISENGAGE, CONFIG_IO,<br />

<strong>and</strong> ACT<strong>IV</strong>E_ENGAGE JTAG <strong>in</strong>structions <strong>in</strong> <strong>Cyclone</strong> <strong>IV</strong> devices.<br />

The chip-wide reset (DEV_CLRn) <strong>and</strong> chip-wide output enable (DEV_OE) p<strong>in</strong>s <strong>in</strong><br />

<strong>Cyclone</strong> <strong>IV</strong> devices do not affect JTAG boundary-scan or programm<strong>in</strong>g operations.<br />

Toggl<strong>in</strong>g these p<strong>in</strong>s do not affect JTAG operations (other than the usual<br />

boundary-scan operation).<br />

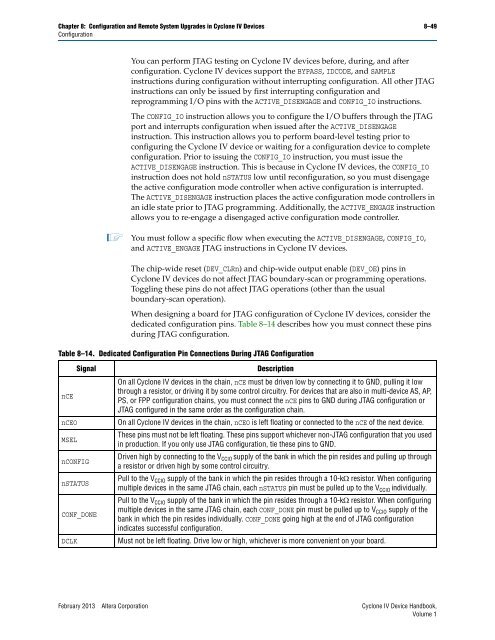

When design<strong>in</strong>g a board for JTAG configuration of <strong>Cyclone</strong> <strong>IV</strong> devices, consider the<br />

dedicated configuration p<strong>in</strong>s. Table 8–14 describes how you must connect these p<strong>in</strong>s<br />

dur<strong>in</strong>g JTAG configuration.<br />

Table 8–14. Dedicated <strong>Configuration</strong> P<strong>in</strong> Connections Dur<strong>in</strong>g JTAG <strong>Configuration</strong><br />

Signal Description<br />

On all <strong>Cyclone</strong> <strong>IV</strong> devices <strong>in</strong> the cha<strong>in</strong>, nCE must be driven low by connect<strong>in</strong>g it to GND, pull<strong>in</strong>g it low<br />

nCE<br />

through a resistor, or driv<strong>in</strong>g it by some control circuitry. For devices that are also <strong>in</strong> multi-device AS, AP,<br />

PS, or FPP configuration cha<strong>in</strong>s, you must connect the nCE p<strong>in</strong>s to GND dur<strong>in</strong>g JTAG configuration or<br />

JTAG configured <strong>in</strong> the same order as the configuration cha<strong>in</strong>.<br />

nCEO On all <strong>Cyclone</strong> <strong>IV</strong> devices <strong>in</strong> the cha<strong>in</strong>, nCEO is left float<strong>in</strong>g or connected to the nCE of the next device.<br />

MSEL<br />

These p<strong>in</strong>s must not be left float<strong>in</strong>g. These p<strong>in</strong>s support whichever non-JTAG configuration that you used<br />

<strong>in</strong> production. If you only use JTAG configuration, tie these p<strong>in</strong>s to GND.<br />

nCONFIG<br />

Driven high by connect<strong>in</strong>g to the VCCIO supply of the bank <strong>in</strong> which the p<strong>in</strong> resides <strong>and</strong> pull<strong>in</strong>g up through<br />

a resistor or driven high by some control circuitry.<br />

nSTATUS<br />

Pull to the VCCIO supply of the bank <strong>in</strong> which the p<strong>in</strong> resides through a 10-k resistor. When configur<strong>in</strong>g<br />

multiple devices <strong>in</strong> the same JTAG cha<strong>in</strong>, each nSTATUS p<strong>in</strong> must be pulled up to the VCCIO <strong>in</strong>dividually.<br />

Pull to the VCCIO supply of the bank <strong>in</strong> which the p<strong>in</strong> resides through a 10-k resistor. When configur<strong>in</strong>g<br />

CONF_DONE<br />

multiple devices <strong>in</strong> the same JTAG cha<strong>in</strong>, each CONF_DONE p<strong>in</strong> must be pulled up to VCCIO supply of the<br />

bank <strong>in</strong> which the p<strong>in</strong> resides <strong>in</strong>dividually. CONF_DONE go<strong>in</strong>g high at the end of JTAG configuration<br />

<strong>in</strong>dicates successful configuration.<br />

DCLK Must not be left float<strong>in</strong>g. Drive low or high, whichever is more convenient on your board.<br />

February 2013 <strong>Altera</strong> Corporation <strong>Cyclone</strong> <strong>IV</strong> Device H<strong>and</strong>book,<br />

Volume 1