Configuration and Remote System Upgrades in Cyclone IV ... - Altera

Configuration and Remote System Upgrades in Cyclone IV ... - Altera

Configuration and Remote System Upgrades in Cyclone IV ... - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

8–74 Chapter 8: <strong>Configuration</strong> <strong>and</strong> <strong>Remote</strong> <strong>System</strong> <strong>Upgrades</strong> <strong>in</strong> <strong>Cyclone</strong> <strong>IV</strong> Devices<br />

<strong>Remote</strong> <strong>System</strong> Upgrade<br />

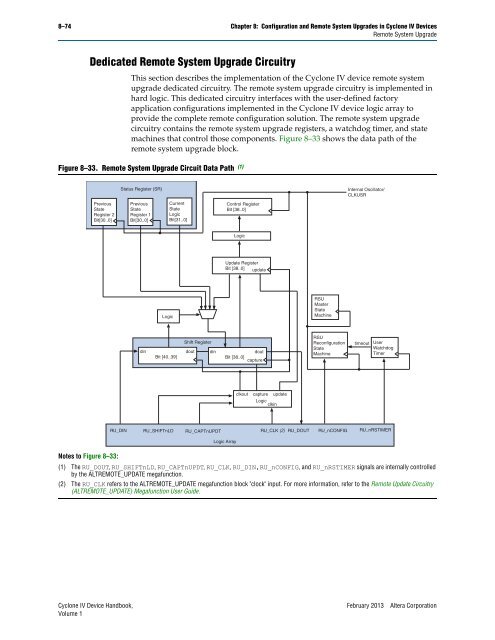

Dedicated <strong>Remote</strong> <strong>System</strong> Upgrade Circuitry<br />

This section describes the implementation of the <strong>Cyclone</strong> <strong>IV</strong> device remote system<br />

upgrade dedicated circuitry. The remote system upgrade circuitry is implemented <strong>in</strong><br />

hard logic. This dedicated circuitry <strong>in</strong>terfaces with the user-def<strong>in</strong>ed factory<br />

application configurations implemented <strong>in</strong> the <strong>Cyclone</strong> <strong>IV</strong> device logic array to<br />

provide the complete remote configuration solution. The remote system upgrade<br />

circuitry conta<strong>in</strong>s the remote system upgrade registers, a watchdog timer, <strong>and</strong> state<br />

mach<strong>in</strong>es that control those components. Figure 8–33 shows the data path of the<br />

remote system upgrade block.<br />

Figure 8–33. <strong>Remote</strong> <strong>System</strong> Upgrade Circuit Data Path (1)<br />

Previous<br />

State<br />

Register 2<br />

Bit[30..0]<br />

Notes to Figure 8–33:<br />

Status Register (SR)<br />

Previous<br />

State<br />

Register 1<br />

Bit[30..0]<br />

d<strong>in</strong><br />

Logic<br />

Bit [40..39]<br />

Current<br />

State<br />

Logic<br />

Bit[31..0]<br />

Shift Register<br />

dout<br />

d<strong>in</strong><br />

Control Register<br />

Bit [38..0]<br />

Logic<br />

Update Register<br />

Bit [38..0] update<br />

dout<br />

Bit [38..0]<br />

capture<br />

clkout capture update<br />

Logic clk<strong>in</strong><br />

Internal Oscillator/<br />

CLKUSR<br />

RU_DIN RU_SHIFTnLD RU_CAPTnUPDT RU_CLK (2) RU_DOUT RU_nCONFIG RU_nRSTIMER<br />

Logic Array<br />

RSU<br />

Master<br />

State<br />

Mach<strong>in</strong>e<br />

RSU<br />

Reconfiguration<br />

State<br />

Mach<strong>in</strong>e<br />

User<br />

Watchdog<br />

Timer<br />

(1) The RU_DOUT, RU_SHIFTnLD, RU_CAPTnUPDT, RU_CLK, RU_DIN,RU_nCONFIG, <strong>and</strong> RU_nRSTIMER signals are <strong>in</strong>ternally controlled<br />

by the ALTREMOTE_UPDATE megafunction.<br />

(2) The RU_CLK refers to the ALTREMOTE_UPDATE megafunction block "clock" <strong>in</strong>put. For more <strong>in</strong>formation, refer to the <strong>Remote</strong> Update Circuitry<br />

(ALTREMOTE_UPDATE) Megafunction User Guide.<br />

<strong>Cyclone</strong> <strong>IV</strong> Device H<strong>and</strong>book, February 2013 <strong>Altera</strong> Corporation<br />

Volume 1<br />

timeout