Configuration and Remote System Upgrades in Cyclone IV ... - Altera

Configuration and Remote System Upgrades in Cyclone IV ... - Altera

Configuration and Remote System Upgrades in Cyclone IV ... - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

8–36 Chapter 8: <strong>Configuration</strong> <strong>and</strong> <strong>Remote</strong> <strong>System</strong> <strong>Upgrades</strong> <strong>in</strong> <strong>Cyclone</strong> <strong>IV</strong> Devices<br />

<strong>Configuration</strong><br />

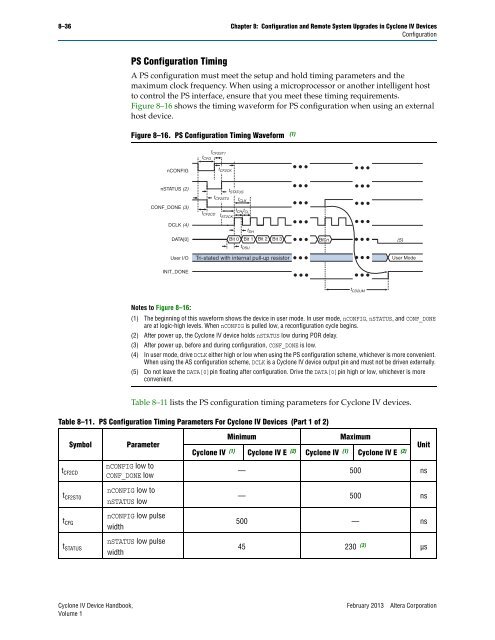

PS <strong>Configuration</strong> Tim<strong>in</strong>g<br />

A PS configuration must meet the setup <strong>and</strong> hold tim<strong>in</strong>g parameters <strong>and</strong> the<br />

maximum clock frequency. When us<strong>in</strong>g a microprocessor or another <strong>in</strong>telligent host<br />

to control the PS <strong>in</strong>terface, ensure that you meet these tim<strong>in</strong>g requirements.<br />

Figure 8–16 shows the tim<strong>in</strong>g waveform for PS configuration when us<strong>in</strong>g an external<br />

host device.<br />

Figure 8–16. PS <strong>Configuration</strong> Tim<strong>in</strong>g Waveform (1)<br />

nCONFIG<br />

nSTATUS (2)<br />

CONF_DONE (3)<br />

DCLK (4)<br />

DATA[0]<br />

User I/O<br />

INIT_DONE<br />

Notes to Figure 8–16:<br />

t CFG<br />

t CF2CD<br />

t CF2ST1<br />

t CF2CK<br />

t CF2ST0<br />

t ST2CK<br />

t STATUS<br />

t CLK<br />

t CH t CL<br />

Bit 0<br />

tDH Bit 1 Bit 2 Bit 3 Bit n<br />

t DSU<br />

Tri-stated with <strong>in</strong>ternal pull-up resistor<br />

(1) The beg<strong>in</strong>n<strong>in</strong>g of this waveform shows the device <strong>in</strong> user mode. In user mode, nCONFIG, nSTATUS, <strong>and</strong> CONF_DONE<br />

are at logic-high levels. When nCONFIG is pulled low, a reconfiguration cycle beg<strong>in</strong>s.<br />

(2) After power up, the <strong>Cyclone</strong> <strong>IV</strong> device holds nSTATUS low dur<strong>in</strong>g POR delay.<br />

(3) After power up, before <strong>and</strong> dur<strong>in</strong>g configuration, CONF_DONE is low.<br />

(4) In user mode, drive DCLK either high or low when us<strong>in</strong>g the PS configuration scheme, whichever is more convenient.<br />

When us<strong>in</strong>g the AS configuration scheme, DCLK is a <strong>Cyclone</strong> <strong>IV</strong> device output p<strong>in</strong> <strong>and</strong> must not be driven externally.<br />

(5) Do not leave the DATA[0]p<strong>in</strong> float<strong>in</strong>g after configuration. Drive the DATA[0]p<strong>in</strong> high or low, whichever is more<br />

convenient.<br />

Table 8–11 lists the PS configuration tim<strong>in</strong>g parameters for <strong>Cyclone</strong> <strong>IV</strong> devices.<br />

Table 8–11. PS <strong>Configuration</strong> Tim<strong>in</strong>g Parameters For <strong>Cyclone</strong> <strong>IV</strong> Devices (Part 1 of 2)<br />

Symbol Parameter<br />

t CF2CD<br />

t CF2ST0<br />

t CFG<br />

t STATUS<br />

nCONFIG low to<br />

CONF_DONE low<br />

nCONFIG low to<br />

nSTATUS low<br />

nCONFIG low pulse<br />

width<br />

nSTATUS low pulse<br />

width<br />

<strong>Cyclone</strong> <strong>IV</strong> Device H<strong>and</strong>book, February 2013 <strong>Altera</strong> Corporation<br />

Volume 1<br />

t CD2UM<br />

M<strong>in</strong>imum Maximum<br />

(5)<br />

User Mode<br />

<strong>Cyclone</strong> <strong>IV</strong> (1) <strong>Cyclone</strong> <strong>IV</strong> E (2) <strong>Cyclone</strong> <strong>IV</strong> (1) <strong>Cyclone</strong> <strong>IV</strong> E (2)<br />

Unit<br />

— 500 ns<br />

— 500 ns<br />

500 — ns<br />

45 230 (3) µs