Service Manual - AMS Neve

Service Manual - AMS Neve

Service Manual - AMS Neve

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

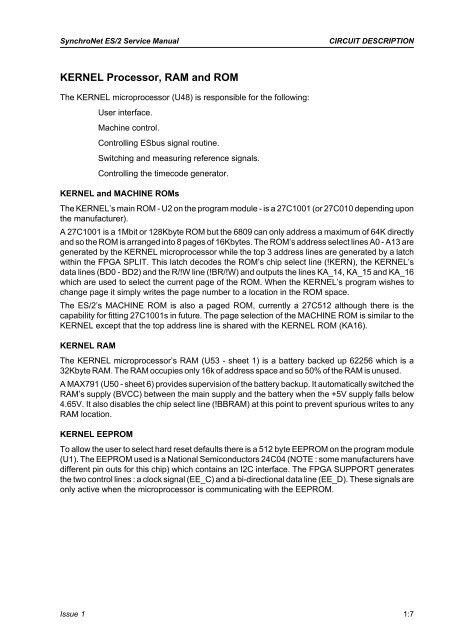

SynchroNet ES/2 <strong>Service</strong> <strong>Manual</strong><br />

CIRCUIT DESCRIPTION<br />

KERNEL Processor, RAM and ROM<br />

The KERNEL microprocessor (U48) is responsible for the following:<br />

<br />

<br />

<br />

<br />

<br />

User interface.<br />

Machine control.<br />

Controlling ESbus signal routine.<br />

Switching and measuring reference signals.<br />

Controlling the timecode generator.<br />

KERNEL and MACHINE ROMs<br />

The KERNEL’s main ROM - U2 on the program module - is a 27C1001 (or 27C010 depending upon<br />

the manufacturer).<br />

A 27C1001 is a 1Mbit or 128Kbyte ROM but the 6809 can only address a maximum of 64K directly<br />

and so the ROM is arranged into 8 pages of 16Kbytes. The ROM’s address select lines A0 - A13 are<br />

generated by the KERNEL microprocessor while the top 3 address lines are generated by a latch<br />

within the FPGA SPLIT. This latch decodes the ROM’s chip select line (!KERN), the KERNEL’s<br />

data lines (BD0 - BD2) and the R/!W line (!BR/!W) and outputs the lines KA_14, KA_15 and KA_16<br />

which are used to select the current page of the ROM. When the KERNEL’s program wishes to<br />

change page it simply writes the page number to a location in the ROM space.<br />

The ES/2’s MACHINE ROM is also a paged ROM, currently a 27C512 although there is the<br />

capability for fitting 27C1001s in future. The page selection of the MACHINE ROM is similar to the<br />

KERNEL except that the top address line is shared with the KERNEL ROM (KA16).<br />

KERNEL RAM<br />

The KERNEL microprocessor’s RAM (U53 - sheet 1) is a battery backed up 62256 which is a<br />

32Kbyte RAM. The RAM occupies only 16k of address space and so 50% of the RAM is unused.<br />

A MAX791 (U50 - sheet 6) provides supervision of the battery backup. It automatically switched the<br />

RAM’s supply (BVCC) between the main supply and the battery when the +5V supply falls below<br />

4.65V. It also disables the chip select line (!BBRAM) at this point to prevent spurious writes to any<br />

RAM location.<br />

KERNEL EEPROM<br />

To allow the user to select hard reset defaults there is a 512 byte EEPROM on the program module<br />

(U1). The EEPROM used is a National Semiconductors 24C04 (NOTE : some manufacturers have<br />

different pin outs for this chip) which contains an I2C interface. The FPGA SUPPORT generates<br />

the two control lines : a clock signal (EE_C) and a bi-directional data line (EE_D). These signals are<br />

only active when the microprocessor is communicating with the EEPROM.<br />

Issue 1 1:7