Service Manual - AMS Neve

Service Manual - AMS Neve

Service Manual - AMS Neve

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

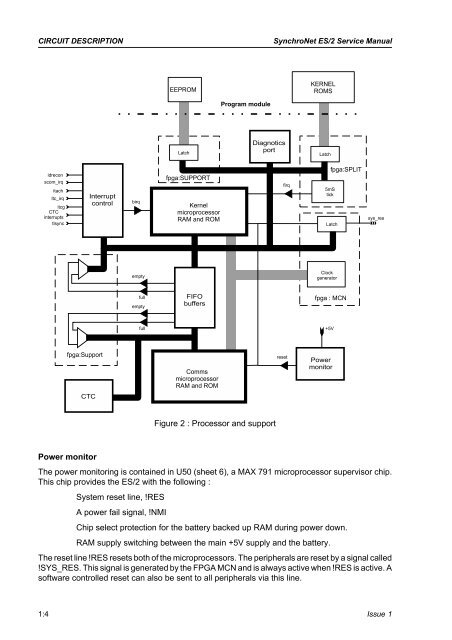

CIRCUIT DESCRIPTION<br />

SynchroNet ES/2 <strong>Service</strong> <strong>Manual</strong><br />

EEPROM<br />

KERNEL<br />

ROMS<br />

Program module<br />

Latch<br />

Diagnotics<br />

port<br />

Latch<br />

idrecon<br />

scom_irq<br />

itach<br />

ltc_irq<br />

itcg<br />

CTC<br />

interrupts<br />

tlsync<br />

Interrupt<br />

control<br />

birq<br />

fpga:SUPPORT<br />

Kernel<br />

microprocessor<br />

RAM and ROM<br />

firq<br />

5mS<br />

tick<br />

fpga:SPLIT<br />

Latch<br />

sys_res<br />

empty<br />

Clock<br />

generator<br />

full<br />

empty<br />

FIFO<br />

buffers<br />

fpga : MCN<br />

full<br />

+5V<br />

fpga:Support<br />

Comms<br />

microprocessor<br />

RAM and ROM<br />

reset<br />

Power<br />

monitor<br />

CTC<br />

Figure 2 : Processor and support<br />

Power monitor<br />

The power monitoring is contained in U50 (sheet 6), a MAX 791 microprocessor supervisor chip.<br />

This chip provides the ES/2 with the following :<br />

<br />

<br />

<br />

<br />

System reset line, !RES<br />

A power fail signal, !NMI<br />

Chip select protection for the battery backed up RAM during power down.<br />

RAM supply switching between the main +5V supply and the battery.<br />

The reset line !RES resets both of the microprocessors. The peripherals are reset by a signal called<br />

!SYS_RES. This signal is generated by the FPGA MCN and is always active when !RES is active. A<br />

software controlled reset can also be sent to all peripherals via this line.<br />

1:4 Issue 1