Service Manual - AMS Neve

Service Manual - AMS Neve

Service Manual - AMS Neve

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

SynchroNet ES/2 <strong>Service</strong> <strong>Manual</strong><br />

CIRCUIT DESCRIPTION<br />

AK ESbus Interface<br />

The ES/2 communicates with controllers and other ES/2s over 1 of 2 ESbus ports, Bus A or Bus B.<br />

Both busses have the following features :<br />

<br />

<br />

<br />

<br />

<br />

<br />

RS422 serial comms ports.<br />

Timeline bus - to distribute a system wide reference square wave.<br />

TLExt line - open collector line to indicate the presence of a timeline master.<br />

Timecode bus - to distribute a system wide timecode stream.<br />

Frame bus - to distribute a system wide video locked square wave<br />

Drec - a Direct Record Line to eliminate serial delays for consistent punch-ins.<br />

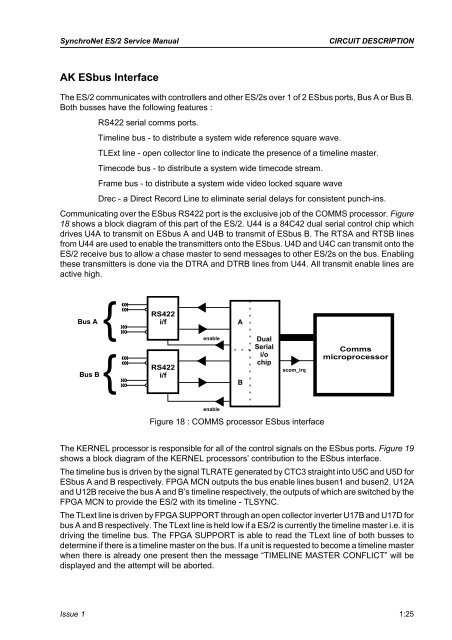

Communicating over the ESbus RS422 port is the exclusive job of the COMMS processor. Figure<br />

18 shows a block diagram of this part of the ES/2. U44 is a 84C42 dual serial control chip which<br />

drives U4A to transmit on ESbus A and U4B to transmit of ESbus B. The RTSA and RTSB lines<br />

from U44 are used to enable the transmitters onto the ESbus. U4D and U4C can transmit onto the<br />

ES/2 receive bus to allow a chase master to send messages to other ES/2s on the bus. Enabling<br />

these transmitters is done via the DTRA and DTRB lines from U44. All transmit enable lines are<br />

active high.<br />

Bus A<br />

{<br />

RS422<br />

i/f<br />

A<br />

Bus B{<br />

RS422<br />

i/f<br />

enable<br />

B<br />

Dual<br />

Serial<br />

i/o<br />

chip<br />

scom_irq<br />

Comms<br />

microprocessor<br />

enable<br />

Figure 18 : COMMS processor ESbus interface<br />

The KERNEL processor is responsible for all of the control signals on the ESbus ports. Figure 19<br />

shows a block diagram of the KERNEL processors’ contribution to the ESbus interface.<br />

The timeline bus is driven by the signal TLRATE generated by CTC3 straight into U5C and U5D for<br />

ESbus A and B respectively. FPGA MCN outputs the bus enable lines busen1 and busen2. U12A<br />

and U12B receive the bus A and B’s timeline respectively, the outputs of which are switched by the<br />

FPGA MCN to provide the ES/2 with its timeline - TLSYNC.<br />

The TLext line is driven by FPGA SUPPORT through an open collector inverter U17B and U17D for<br />

bus A and B respectively. The TLext line is held low if a ES/2 is currently the timeline master i.e. it is<br />

driving the timeline bus. The FPGA SUPPORT is able to read the TLext line of both busses to<br />

determine if there is a timeline master on the bus. If a unit is requested to become a timeline master<br />

when there is already one present then the message “TIMELINE MASTER CONFLICT” will be<br />

displayed and the attempt will be aborted.<br />

Issue 1 1:25