Service Manual - AMS Neve

Service Manual - AMS Neve

Service Manual - AMS Neve

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

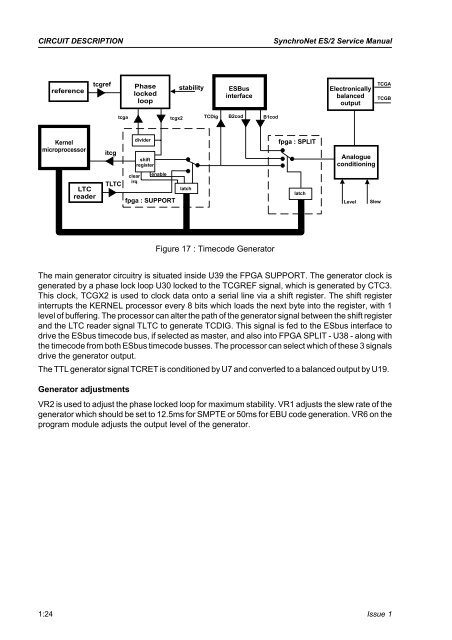

CIRCUIT DESCRIPTION<br />

SynchroNet ES/2 <strong>Service</strong> <strong>Manual</strong><br />

reference<br />

tcgref<br />

Phase<br />

locked<br />

loop<br />

stability<br />

ESBus<br />

interface<br />

Electronically<br />

balanced<br />

output<br />

TCGA<br />

TCGB<br />

tcga<br />

tcgx2<br />

TCDig<br />

B2cod<br />

B1cod<br />

Kernel<br />

microprocessor<br />

itcg<br />

divider<br />

shift<br />

register<br />

fpga : SPLIT<br />

Analogue<br />

conditioning<br />

LTC<br />

reader<br />

TLTC<br />

clear<br />

irq<br />

enable<br />

fpga:SUPPORT<br />

latch<br />

latch<br />

Level<br />

Slew<br />

Figure 17 : Timecode Generator<br />

The main generator circuitry is situated inside U39 the FPGA SUPPORT. The generator clock is<br />

generated by a phase lock loop U30 locked to the TCGREF signal, which is generated by CTC3.<br />

This clock, TCGX2 is used to clock data onto a serial line via a shift register. The shift register<br />

interrupts the KERNEL processor every 8 bits which loads the next byte into the register, with 1<br />

level of buffering. The processor can alter the path of the generator signal between the shift register<br />

and the LTC reader signal TLTC to generate TCDIG. This signal is fed to the ESbus interface to<br />

drive the ESbus timecode bus, if selected as master, and also into FPGA SPLIT - U38 - along with<br />

the timecode from both ESbus timecode busses. The processor can select which of these 3 signals<br />

drive the generator output.<br />

The TTL generator signal TCRET is conditioned by U7 and converted to a balanced output by U19.<br />

Generator adjustments<br />

VR2 is used to adjust the phase locked loop for maximum stability. VR1 adjusts the slew rate of the<br />

generator which should be set to 12.5ms for SMPTE or 50ms for EBU code generation. VR6 on the<br />

program module adjusts the output level of the generator.<br />

1:24 Issue 1