Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

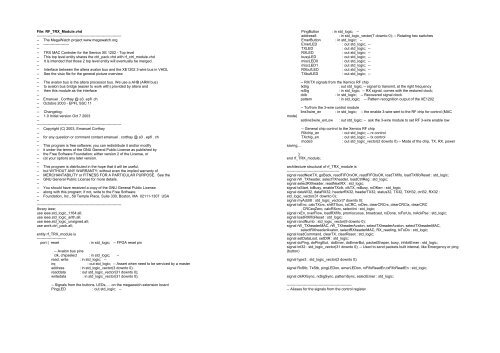

File: RF_TRX_Module.vhd----------------------------------------------------------------------- The MegaWatch project www.megawatch.org-- ------------------------- TRX MAC Controler <strong>for</strong> the Xemics XE 1202 - Top level-- This top level entity shares the ctrl_pack.vhd with rf_ctrl_module.vhd-- It is intended that those 2 top level entity will eventually be merged.---- Interface between the altera avalon bus <strong>and</strong> the XE1202 3-wire bus in VHDL-- See the visio file <strong>for</strong> the general picture overview---- The avalon bus is the altera processor bus. We use a AHB (ARM bus)-- to avalon bus bridge (easier to work with) provided by altera <strong>and</strong>-- then this module as the interface---- Emanuel . Corthay @ a3. epfl .ch-- Octobre 2003 - EPFL SSC 11---- Changelog:-- 1.0 Initial version Oct 7 2003------------------------------------------------------------------------- Copyright (C) 2003, Emanuel Corthay---- <strong>for</strong> any question or comment contact emanuel . corthay @ a3 . epfl . ch---- This program is free s<strong>of</strong>tware; you can redistribute it <strong>and</strong>/or modify-- it under the terms <strong>of</strong> the GNU General Public License as published by-- the Free S<strong>of</strong>tware Foundation; either version 2 <strong>of</strong> the License, or-- (at your option) any later version.---- This program is distributed in the hope that it will be useful,-- but WITHOUT ANY WARRANTY; without even the implied warranty <strong>of</strong>-- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the-- GNU General Public License <strong>for</strong> more details.---- You should have received a copy <strong>of</strong> the GNU General Public License-- along with this program; if not, write to the Free S<strong>of</strong>tware-- Foundation, Inc., 59 Temple Place, Suite 330, Boston, MA 02111-1307 USA-----------------------------------------------------------------------library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;use work.ctrl_pack.all;entity rf_TRX_module is------------------------port ( reset: in std_logic; -- FPGA reset pin-- Avalon bus pinsclk, chipselect : in std_logic; --read, write : in std_logic; --irq : out std_logic; -- Assert when need to be serviced by a masteraddress : in std_logic_vector(3 downto 0);readdata : out std_logic_vector(31 downto 0);writedata : in std_logic_vector(31 downto 0);-- Signals from the buttons, LEDs, ... on the megawatch extension boardPingLED : out std_logic; --mode)PingButton : in std_logic; --address8: in std_logic_vector(7 downto 0); -- Rotating hex switchesEmerButton : in std_logic; --EmerLED : out std_logic; --TXLED : out std_logic; --RXLED : out std_logic; --busyLED : out std_logic; --miscLED0 : out std_logic; --miscLED1 : out std_logic; --RXbufLED : out std_logic; --TXbufLED : out std_logic; ---- RX/TX signals from the Xemics RF chiptxSig: out std_logic; -- signal to transmit, at the right frequencyrxSig: in std_logic; -- RX signal, comes with the restored clock;dclk: in std_logic; -- Recovered signal clockpattern: in std_logic; -- Pattern recognition output <strong>of</strong> the XE1202-- To/from the 3-wire control moduleline3wire_en : in std_logic; -- the enable 3-wire sent to the RF chip <strong>for</strong> control (MACsetline3wire_enLow : out std_logic; -- ask the 3-wire module to set RF 3-wire enable low-- General chip control to the Xemics RF chipRXchip_en: out std_logic; -- rx controlTXchip_en: out std_logic; -- tx controlmode3: out std_logic_vector(2 downto 0) -- Mode <strong>of</strong> the chip, TX, RX, powersaving,...);end rf_TRX_module;architecture structural <strong>of</strong> rf_TRX_module is-------------------------------------------signal readNextTX, goBack, readFIFOrxOK, readFIFOtxOK, loadTXfifo, loadTXfifoReset : std_logic;signal rW_TXheader, selectTXheader, loadCtrlReg : std_logic;signal selectRXheader, readNextRX : std_logic;signal txStart, txBusy, enableTXclk, clkTX, rxBusy, rxOKerr : std_logic;signal dataW32, dataRX32, headerRX32, headerTX32, status32, TX32, TXH32, ctrl32, RX32 :std_logic_vector(31 downto 0);signal myAddr8 : std_logic_vector(7 downto 0);signal txEnc, calcTXcrc, shiftTXcrc, txCRC, rxDec, clearCRCrx, clearCRCtx, clearCRC, CRCeqZero, calcRXcrc, selectInt : std_logic;signal rxEn, overFlow, loadRXfifo, promiscuous, broadcast, rxDone, rxForUs, rxAckPse : std_logic;signal loadRXfifoReset : std_logic;signal r<strong>and</strong>Numb : std_logic_vector(9 downto 0);signal rW_TXheaderMAC, rW_TXheaderAvalon, selectTXheaderAvalon, selectTXheaderMAC,selectRXheaderAvalon, selectRXheaderMAC, RX_reading, txToDo : std_logic;signal loadComm<strong>and</strong>, clearTX, clearReset : std_logic;signal setDataLost, setDtR : std_logic;signal doPing, doPingBut, doEmer, doEmerBut, packetShaper, busy, inhibitEmer : std_logic;signal int32 : std_logic_vector(31 downto 0); -- Used to send packets built internal, like Emergency or ping(button)signal type3 : std_logic_vector(2 downto 0);signal RxStb, TxStb, pingLEDon, emerLEDon, rxFifoReadEn,txFifoReadEn : std_logic;signal clkRXsync, rxSigSync, patternSync, selectEmer : std_logic;------------------------------------------------------- Aliases <strong>for</strong> the signals from the control register