Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

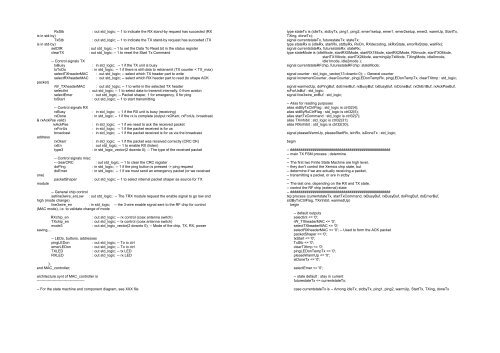

RxStbis in std-by)TxStbis in std-by)setDtRclearTX: out std_logic; -- 1 to indicate the RX st<strong>and</strong>-by request has succeded (RX: out std_logic; -- 1 to indicate the TX st<strong>and</strong>-by request has succeded (TX: out std_logic; -- 1 to set the Data To Read bit in the status register: out std_logic; -- 1 to reset the Start Tx Comm<strong>and</strong>-- Control signals TXtxBusy: in std_logic; -- 1 if the TX unit is busytxToDo: in std_logic; -- 1 if there is still data to retransmit (TX counter < TX_max)selectTXheaderMAC : out std_logic; -- select which TX header part to writeselectRXheaderMAC : out std_logic; -- select which RX header part to read (to shape ACKpacket)rW_TXheaderMAC : out std_logic; -- 1 to write in the selected TX headerselectInt: out std_logic; -- 1 to select data to transmit internally, 0 from avalonselectEmer: out std_logic; -- Packet shaper, 1 <strong>for</strong> emergency, 0 <strong>for</strong> pingtxStart: out std_logic; -- 1 to start transmitting-- Control signals RXrxBusyrxDone& rxAckPse valid)rxAckPserxForUsbroadcastaddressrxOkerrrxEntype3one)module: in std_logic; -- 1 if the RX unit is busy (receiving): in std_logic; -- 1 if the rx is complete (output rxOKerr, rxForUs, broadcast: in std_logic; -- 1 if we need to ack the received packet: in std_logic; -- 1 if the packet received is <strong>for</strong> us: in std_logic; -- 1 if the packet received is <strong>for</strong> us via the broadcast: in std_logic; -- 1 if the packet was received correctly (CRC OK): out std_logic; -- 1 to enable RX (listen): in std_logic_vector(2 downto 0); -- The type <strong>of</strong> the received packet-- Control signals misc-- clearCRC : out std_logic; -- 1 to clear the CRC registerdoPing: in std_logic; -- 1 if the ping button is pressed -> ping requestdoEmer: in std_logic; -- 1 if we must send an emergency packet (or we receivedpacketShaper: out std_logic; -- 1 to select internal packet shaper as source <strong>for</strong> TX-- General chip controlsetline3wire_enLow : out std_logic; -- The TRX module request the enable signal to go low <strong>and</strong>high (mode change)line3wire_en : in std_logic; -- the 3-wire enable signal sent to the RF chip <strong>for</strong> control(MAC mode), i.e. to validate change <strong>of</strong> modeRXchip_enTXchip_enmode3saving,...: out std_logic; -- rx control (coax antenna switch): out std_logic; -- tx control (coax antenna switch): out std_logic_vector(2 downto 0); -- Mode <strong>of</strong> the chip, TX, RX, power-- LEDs, buttons, addressespingLEDon: out std_logic; -- To io ctrlemerLEDon: out std_logic; -- To io ctrlTXLED: out std_logic; -- tx LEDRXLED: out std_logic -- rx LED);end MAC_controller;architecture synt <strong>of</strong> MAC_controller is----------------------------------------- For the state machine <strong>and</strong> component diagram, see XXX filetype stateTx is (idleTx, stdbyTx, ping1, ping2, emer1setup, emer1, emer2setup, emer2, warmUp, StartTx,TXing, doneTx);signal currentstateTx, futurestateTx: stateTx;type stateRx is (idleRx, startRx, stdbyRx, RxOn, RXdecoding, okRxState, errorRxState, waitRx);signal currentstateRx, futurestateRx: stateRx;type stateMode is (idleMode, startRX0Mode, startRX1Mode, startRX2Mode, RXmode, startTX0Mode,startTX1Mode, startTX2Mode, warmingUpTxMode, TXingMode, idle0mode,idle1mode, idle2mode );signal currentstateRFchip, futurestateRFchip: stateMode;signal counter : std_logic_vector(13 downto 0); -- General countersignal incrementCounter, clearCounter, pingLEDonTempRx, pingLEDonTempTx, clearTXtmp : std_logic;signal warmedUp, doPingBuf, doEmerBuf, rxBusyBuf, txBusyBuf, rxDoneBuf, rxOkErrBuf, rxAckPseBuf,rxForUsBuf : std_logic;signal line3wire_enBuf : std_logic;-- Alias <strong>for</strong> reading purposesalias stdByTxCtrlFlag : std_logic is ctrl32(4);alias stdByRxCtrlFlag : std_logic is ctrl32(5);alias startTxComm<strong>and</strong> : std_logic is ctrl32(7);alias TXinhibit : std_logic is ctrl32(31);alias RXinhibit : std_logic is ctrl32(30);signal pleaseWarmUp, pleaseStartRx, isInRx, isDoneTx : std_logic;begin-- #################################################-- main TX FSM process ; determine---- The first two Finite State Machine are high level,-- they don't control the Xemics chip state, but-- determine if we are actually receiving a packet,-- transmitting a packet, or are in stdby---- The last one, depending on the RX <strong>and</strong> TX state,-- control the RF chip (external) state-- #################################################txp:process (currentstateTx, startTxComm<strong>and</strong>, txBusyBuf, rxBusyBuf, doPingBuf, doEmerBuf,stdByTxCtrlFlag, TXinhibit, warmedUp)begin-- default outputsselectInt