Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

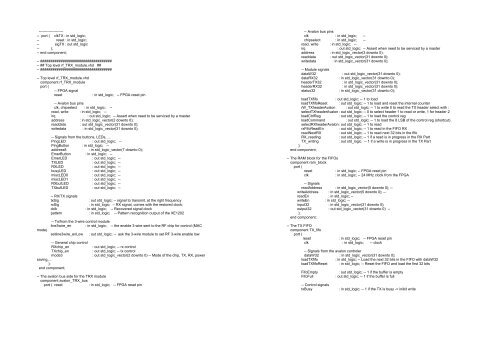

---------------------- port ( clkTX : in std_logic;-- reset : in std_logic;-- sigTX : out std_logic-- );-- end component;-- ###################################-- ## Top level rf_TRX_module.vhd ##-- ###################################-- Top level rf_TRX_module.vhdcomponent rf_TRX_moduleport (-- FPGA signalresetmode): in std_logic; -- FPGA reset pin-- Avalon bus pinsclk, chipselect : in std_logic; --read, write : in std_logic; --irq : out std_logic; -- Assert when need to be serviced by a masteraddress : in std_logic_vector(2 downto 0);readdata : out std_logic_vector(31 downto 0);writedata : in std_logic_vector(31 downto 0);-- Signals from the buttons, LEDs, ...PingLED : out std_logic; --PingButton : in std_logic; --address8 : in std_logic_vector(7 downto 0);EmerButton : in std_logic; --EmerLED : out std_logic; --TXLED : out std_logic; --RXLED : out std_logic; --busyLED : out std_logic; --miscLED0 : out std_logic; --miscLED1 : out std_logic; --RXbufLED : out std_logic; --TXbufLED : out std_logic; ---- RX/TX signalstxSigrxSigdclkpattern: out std_logic; -- signal to transmit, at the right frequency: in std_logic; -- RX signal, comes with the restored clock;: in std_logic; -- Recovered signal clock: in std_logic; -- Pattern recognition output <strong>of</strong> the XE1202-- To/from the 3-wire control moduleline3wire_en : in std_logic; -- the enable 3-wire sent to the RF chip <strong>for</strong> control (MACsetline3wire_enLow : out std_logic; -- ask the 3-wire module to set RF 3-wire enable low-- General chip controlRXchip_enTXchip_enmode3saving,...);end component;-- The avalon bus side <strong>for</strong> the TRX modulecomponent avalon_TRX_busport ( reset: in std_logic; -- FPGA reset pin: out std_logic; -- rx control: out std_logic; -- tx control: out std_logic_vector(2 downto 0) -- Mode <strong>of</strong> the chip, TX, RX, power-- Avalon bus pinsclk : in std_logic; --chipselect : in std_logic; --read, write : in std_logic; --irq : out std_logic; -- Assert when need to be serviced by a masteraddress : in std_logic_vector(3 downto 0);readdata : out std_logic_vector(31 downto 0);writedata : in std_logic_vector(31 downto 0);-- Module signalsdataW32 : out std_logic_vector(31 downto 0);dataRX32 : in std_logic_vector(31 downto 0);headerTX32 : in std_logic_vector(31 downto 0);headerRX32 : in std_logic_vector(31 downto 0);status32 : in std_logic_vector(31 downto 0);loadTXfifo : out std_logic; -- 1 to loadloadTXfifoReset : out std_logic; -- 1 to load <strong>and</strong> reset the internal counterrW_TXheaderAvalon : out std_logic; -- 1 to write 0 to read the TX header select with :selectTXheaderAvalon : out std_logic; -- 0 to select header 1 to read or write, 1 <strong>for</strong> header 2loadCtrlReg : out std_logic; -- 1 to load the control regloadComm<strong>and</strong>: out std_logic; -- 1 to load the 8 LSB <strong>of</strong> the control reg (shortcut)selectRXheaderAvalon : out std_logic; -- 1 to readrxFifoReadEn : out std_logic; -- 1 to read in the FIFO RXreadNextRX : out std_logic; -- 1 to read next 32 bits in the fifoRX_reading : out std_logic; -- 1 if a read is in progress in the RX PartTX_writing: out std_logic -- 1 if a write is in progress in the TX Part);end component;-- The RAM block <strong>for</strong> the FIFOscomponent ram_blockport (reset: in std_logic; -- FPGA reset pinclk: in std_logic; -- 24 MHz clock from the FPGA-- SignalsreadAddress : in std_logic_vector(5 downto 0); --writeAddress : in std_logic_vector(5 downto 0); --readEn : in std_logic; --writeEn : in std_logic; --input32 : in std_logic_vector(31 downto 0);output32 : out std_logic_vector(31 downto 0) --);end component;-- The TX FIFOcomponent TX_fifoport (resetclk: in std_logic; -- FPGA reset pin: in std_logic; -- clock-- Signals from the avalon controlerdataW32 : in std_logic_vector(31 downto 0);loadTXfifo : in std_logic; -- Load the next 32 bits in the FIFO with dataW32loadTXfifoReset : in std_logic; -- Reset the FIFO <strong>and</strong> load the first 32 bitsFifoEmptyFifoFull-- Control signalstxBusy: out std_logic; -- 1 if the buffer is empty: out std_logic; -- 1 if the buffer is full: in std_logic; -- 1 if the TX is busy -> inibit write