Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

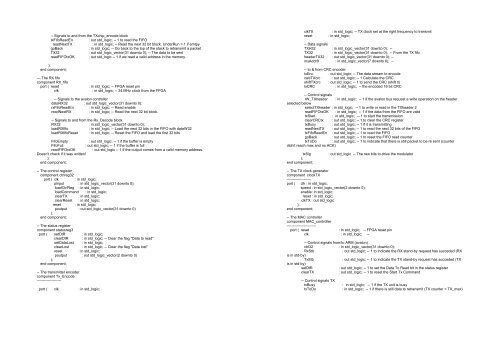

-- Signals to <strong>and</strong> from the TXchip_encode blocktxFifoReadEn : out std_logic; -- 1 to read the FIFOreadNextTX: in std_logic; -- Read the next 32 bit block. UnderRun = 1 if emtpygoBack: in std_logic; -- Go back to the top <strong>of</strong> the stack to retransmit a packetTX32: out std_logic_vector(31 downto 0); -- The data to be sentreadFIFOtxOK : out std_logic -- 1 if we read a valid address in the memory.);end component;--- The RX fifocomponent RX_fifoport ( resetclk: in std_logic; -- FPGA reset pin: in std_logic; -- 24 MHz clock from the FPGA-- Signals to the avalon controllerdataRX32 : out std_logic_vector(31 downto 0);rxFifoReadEn : in std_logic; -- Read enablereadNextRX : in std_logic; -- Read the next 32 bit block.-- Signals to <strong>and</strong> from the Rx_Decode blockRX32 : in std_logic_vector(31 downto 0);loadRXfifo: in std_logic; -- Load the next 32 bits in the FIFO with dataW32loadRXfifoReset : in std_logic; -- Reset the FIFO <strong>and</strong> load the first 32 bitsFifoEmpty: out std_logic; -- 1 if the buffer is emptyFifoFull: out std_logic; -- 1 if the buffer is fullreadFIFOrxOK : out std_logic -- 1 if the output comes from a valid memory address.Doesn't check if it was written!);end component;-- The control registercomponent ctrlreg32port ( clk : in std_logic;pinput : in std_logic_vector(31 downto 0);loadCtrlReg : in std_logic;loadComm<strong>and</strong> : in std_logic;clearTX : in std_logic;clearReset : in std_logic;reset : in std_logic;poutput : out std_logic_vector(31 downto 0));end component;-- The status registercomponent statusreg3port ( setDtR : in std_logic;clearDtR : in std_logic; -- Clear the flag "Data to read"setDataLost : in std_logic;clearLost : in std_logic; -- Clear the flag "Data lost"reset : in std_logic;);end component;poutput : out std_logic_vector(2 downto 0)-- The transmitter encodercomponent Tx_Encode--------------------port ( clk: in std_logic;clkTXreset: in std_logic; -- TX clock set at the right frequency to transmit: in std_logic;-- Data signalsTXH32 : in std_logic_vector(31 downto 0); --TX32: in std_logic_vector(31 downto 0); -- From the TX fifoheaderTX32 : out std_logic_vector(31 downto 0); --myAddr8 : in std_logic_vector(7 downto 0); ---- to & from CRC encodertxEnc : out std_logic; -- The data stream to encodecalcTXcrc : out std_logic; -- 1 Calculate the CRCshiftTXcrc : out std_logic; -- 1 to send the CRC (shift it)txCRC: in std_logic; -- the encoded 16 bit CRC-- Control signalsrW_TXheader : in std_logic; -- 1 if the avalon bus request a write operation on the headerselected belowselectTXheader : in std_logic; -- 1 to write or read in the TXheader 2readFIFOtxOK : in std_logic; -- 1 if the data from the FIFO are validtxStart : in std_logic; -- 1 to start the transmissionclearCRCtx : out std_logic; -- 1 to clear the CRC registertxBusy : out std_logic; -- 1 if it is transmittingreadNextTX : out std_logic; -- 1 to read the next 32 bits <strong>of</strong> the FIFOtxFifoReadEn : out std_logic; -- 1 to read the FIFOgoBack : out std_logic; -- 1 to reset the FIFO read countertxToDo : out std_logic; -- 1 to indicate that there is still packet to be re sent (counterdidn't reach max <strong>and</strong> no ACK)txSig);end component;-- The TX clock generatorcomponent clockTX--------------------port ( clk : in std_logic;speed : in std_logic_vector(2 downto 0);enable: in std_logic;reset : in std_logic;clkTX : out std_logic);end component;: out std_logic -- The raw bits to drive the modulator-- The MAC controllercomponent MAC_controller------------------------port ( reset: in std_logic; -- FPGA reset pinclk : in std_logic; ---- Control signals from/to ARM (avalon)ctrl32 : in std_logic_vector(31 downto 0);RxStb: out std_logic; -- 1 to indicate the RX st<strong>and</strong>-by request has succeded (RXis in std-by)TxStb: out std_logic; -- 1 to indicate the TX st<strong>and</strong>-by request has succeded (TXis in std-by)setDtR: out std_logic; -- 1 to set the Data To Read bit in the status registerclearTX: out std_logic; -- 1 to reset the Start Tx Comm<strong>and</strong>-- Control signals TXtxBusytxToDo: in std_logic; -- 1 if the TX unit is busy: in std_logic; -- 1 if there is still data to retransmit (TX counter < TX_max)