Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

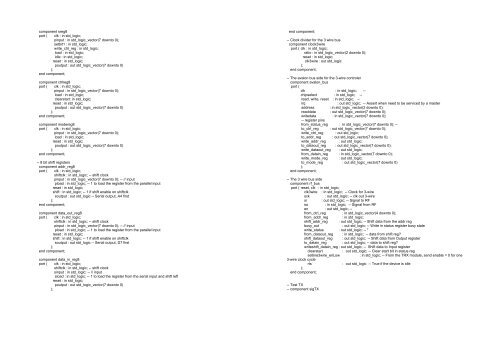

component sreg8port ( clk : in std_logic;pinput : in std_logic_vector(7 downto 0);setbit1 : in std_logic;write_ctrl_reg : in std_logic;load : in std_logic;idle : in std_logic;reset : in std_logic;poutput : out std_logic_vector(7 downto 0));end component;component ctrlreg8port ( clk : in std_logic;pinput : in std_logic_vector(7 downto 0);load : in std_logic;clearstart: in std_logic;reset : in std_logic;poutput : out std_logic_vector(7 downto 0));end component;component modereg8port ( clk : in std_logic;pinput : in std_logic_vector(7 downto 0);load : in std_logic;reset : in std_logic;poutput : out std_logic_vector(7 downto 0));end component;-- 8 bit shift registerscomponent addr_reg8port ( clk : in std_logic;shiftclk : in std_logic; -- shift clockpinput : in std_logic_vector(7 downto 0); -- // inputpload : in std_logic; -- 1 to load the register from the parallel inputreset : in std_logic;shift : in std_logic; -- 1 if shift enable on shiftclksoutput : out std_logic -- Serial output, A4 first);end component;component data_out_reg8port ( clk : in std_logic;shiftclk : in std_logic; -- shift clockpinput : in std_logic_vector(7 downto 0); -- // inputpload : in std_logic; -- 1 to load the register from the parallel inputreset : in std_logic;shift : in std_logic; -- 1 if shift enable on shiftclksoutput : out std_logic -- Serial output, D7 first);end component;component data_in_reg8port ( clk : in std_logic;shiftclk : in std_logic; -- shift clocksinput : in std_logic; -- // inputsload : in std_logic; -- 1 to load the register from the serial input <strong>and</strong> shift leftreset : in std_logic;poutput : out std_logic_vector(7 downto 0));end component;-- Clock divider <strong>for</strong> the 3 wire buscomponent clock3wireport ( clk : in std_logic;ratio : in std_logic_vector(2 downto 0);reset : in std_logic;clk3wire : out std_logic);end component;-- The avalon bus side <strong>for</strong> the 3-wire controlercomponent avalon_busport (clk : in std_logic; --chipselect : in std_logic; --read, write, reset : in std_logic; --irq : out std_logic; -- Assert when need to be serviced by a masteraddress : in std_logic_vector(2 downto 0);readdata : out std_logic_vector(7 downto 0);writedata : in std_logic_vector(7 downto 0);-- register pinsfrom_status_reg : in std_logic_vector(7 downto 0); --to_ctrl_reg : out std_logic_vector(7 downto 0);write_ctrl_reg : out std_logic;to_addr_reg : out std_logic_vector(7 downto 0);write_addr_reg : out std_logic;to_dataout_reg : out std_logic_vector(7 downto 0);write_dataout_reg : out std_logic;from_datain_reg : in std_logic_vector(7 downto 0);write_mode_reg : out std_logic;to_mode_reg : out std_logic_vector(7 downto 0));end component;-- The 3 wire bus sidecomponent rf_busport ( reset, clk : in std_logic;clk3wire : in std_logic; -- Clock <strong>for</strong> 3-wiresck : out std_logic; -- clk out 3-wiresi : out std_logic; -- Signal to RFso : in std_logic; -- Signal from RFen : out std_logic; --from_ctrl_reg : in std_logic_vector(4 downto 0);from_addr_reg : in std_logic;shift_addr_reg : out std_logic; -- Shift data from the addr regbusy_out: out std_logic; -- Write in status register busy statewrite_status : out std_logic; -- "from_dataout_reg : in std_logic; -- data from shift reg?shift_dataout_reg : out std_logic; -- Shift data from Output registerto_datain_reg : out std_logic; -- data to shift reg?writeshift_datain_reg : out std_logic; -- Shift data to Input registerclearstart: out std_logic; -- Clear start bit in status regsetline3wire_enLow: in std_logic; -- From the TRX module, send enable = 0 <strong>for</strong> one3-wire clock cyclerts: out std_logic -- True if the device is idle);end component;-- Test TX-- component sigTX