Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

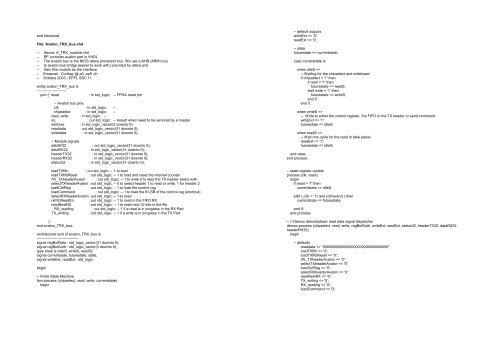

end structural;File: Avalon_TRX_bus.vhd-- Above: rf_TRX_module.vhd-- RF controler avalon part in VHDL-- The avalon bus is the NIOS altera processor bus. We use a AHB (ARM bus)-- to avalon bus bridge (easier to work with) provided by altera <strong>and</strong>-- then this module as the interface-- Emanuel . Corthay @ a3. epfl .ch-- Octobre 2003 - EPFL SSC 11entity avalon_TRX_bus is------------------------port ( reset: in std_logic; -- FPGA reset pin-- Avalon bus pinsclk : in std_logic; --chipselect : in std_logic; --read, write : in std_logic; --irq : out std_logic; -- Assert when need to be serviced by a masteraddress : in std_logic_vector(3 downto 0);readdata : out std_logic_vector(31 downto 0);writedata : in std_logic_vector(31 downto 0);-- Module signalsdataW32 : out std_logic_vector(31 downto 0);dataRX32 : in std_logic_vector(31 downto 0);headerTX32 : in std_logic_vector(31 downto 0);headerRX32 : in std_logic_vector(31 downto 0);status32 : in std_logic_vector(31 downto 0);loadTXfifo : out std_logic; -- 1 to loadloadTXfifoReset : out std_logic; -- 1 to load <strong>and</strong> reset the internal counterrW_TXheaderAvalon : out std_logic; -- 1 to write 0 to read the TX header select with :selectTXheaderAvalon : out std_logic; -- 0 to select header 1 to read or write, 1 <strong>for</strong> header 2loadCtrlReg : out std_logic; -- 1 to load the control regloadComm<strong>and</strong>: out std_logic; -- 1 to load the 8 LSB <strong>of</strong> the control reg (shortcut)selectRXheaderAvalon : out std_logic; -- 1 to readrxFifoReadEn : out std_logic; -- 1 to read in the FIFO RXreadNextRX : out std_logic; -- 1 to read next 32 bits in the fifoRX_reading: out std_logic; -- 1 if a read is in progress in the RX PartTX_writing: out std_logic -- 1 if a write is in progress in the TX Part);end avalon_TRX_bus;architecture synt <strong>of</strong> avalon_TRX_bus is----------------------------------signal regBufData : std_logic_vector(31 downto 0);signal regBufAddr : std_logic_vector(3 downto 0);type state is (idleS, writeS, readS);signal currentstate, futurestate: state;signal writeExt, readExt: std_logic;begin-- Finite State Machinefsm:process (chipselect, read, write, currentstate)begin-- default outputswriteExt