Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

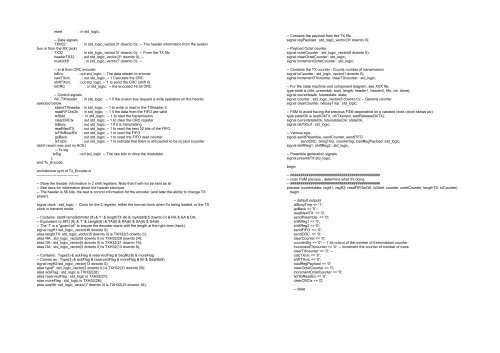

eset : in std_logic;-- Data signalsTXH32 : in std_logic_vector(31 downto 0); -- The header in<strong>for</strong>mation from the avalonbus or from the RX (ack)TX32: in std_logic_vector(31 downto 0); -- From the TX fifoheaderTX32 : out std_logic_vector(31 downto 0); --myAddr8 : in std_logic_vector(7 downto 0); ---- to & from CRC encodertxEnc : out std_logic; -- The data stream to encodecalcTXcrc : out std_logic; -- 1 Calculate the CRCshiftTXcrc : out std_logic; -- 1 to send the CRC (shift it)txCRC: in std_logic; -- the encoded 16 bit CRC-- Control signalsrW_TXheader : in std_logic; -- 1 if the avalon bus request a write operation on the headerselected belowselectTXheader : in std_logic; -- 1 to write or read in the TXheader 2readFIFOtxOk : in std_logic; -- 1 if the data from the FIFO are validtxStart : in std_logic; -- 1 to start the transmissionclearCRCtx : out std_logic; -- 1 to clear the CRC registertxBusy : out std_logic; -- 1 if it is transmittingreadNextTX : out std_logic; -- 1 to read the next 32 bits <strong>of</strong> the FIFOtxFifoReadEn : out std_logic; -- 1 to read the FIFOgoBack : out std_logic; -- 1 to reset the FIFO read countertxToDo : out std_logic; -- 1 to indicate that there is still packet to be re sent (counterdidn't reach max <strong>and</strong> no ACK)-- Tx sigtxSig : out std_logic -- The raw bits to drive the modulator);end Tx_Encode;architecture synt <strong>of</strong> Tx_Encode is------------------------------------ Store the header in<strong>for</strong>mation in 2 shift registers. Note that it will not be sent as is!-- See docs <strong>for</strong> in<strong>for</strong>mation about the header structure-- The header is 56 bits, the rest is control in<strong>for</strong>mation <strong>for</strong> the encoder (<strong>and</strong> later the ability to change TXpower).signal clock : std_logic; -- Clock <strong>for</strong> the 2 register, either the normal clock when it's being loaded, or the TXclock in transmit mode-- Contains: startFrameDelimiter (8) & '1' & lengthTX (6) & myAddr8(5 downto 0) & RA & SA & DA;-- Equivalent to SFD (8) & '1' & Length(6) & TA(6) & RA(6) & SA(6) & DA(6)-- The '1' is a "guard bit" to ensure the decoder starts with the length at the right time (hack)signal regH1:std_logic_vector(46 downto 0);alias lengthTX: std_logic_vector(5 downto 0) is TXH32(5 downto 0);alias RA : std_logic_vector(5 downto 0) is TXH32(29 downto 24);alias SA : std_logic_vector(5 downto 0) is TXH32(21 downto 16);alias DA : std_logic_vector(5 downto 0) is TXH32(13 downto 8);-- Contains: Type(3) & ackFlag & reservedFlag & SeqNb(8) & moreFlag-- Comes as : Type(3) & ackFlag & reservedFlag & moreFlag & 00 & SeqNb(8)signal regH2:std_logic_vector(13 downto 0);alias typeF :std_logic_vector(2 downto 0) is TXH32(31 downto 29);alias ackFlag : std_logic is TXH32(28);alias reservedFlag : std_logic is TXH32(27);alias moreFlag : std_logic is TXH32(26);alias seqNb: std_logic_vector(7 downto 0) is TXH32(23 downto 16);-- Contains the payload from the TX fifosignal regPayload : std_logic_vector(31 downto 0);-- Payload Octet countersignal octetCounter : std_logic_vector(6 downto 0);signal clearOctetCounter : std_logic;signal incrementOctetCounter : std_logic;-- Contains the TX counter : Counts number <strong>of</strong> transmissionsignal txCounter : std_logic_vector(1 downto 0);signal incrementTXcounter, clearTXcounter : std_logic;-- For the state machine <strong>and</strong> component diagram, see XXX filetype state is (idle, preamble, start, length, header1, header2, fifo, crc, done);signal currentstate, futurestate: state;signal counter : std_logic_vector(8 downto 0); -- General countersignal clearCounter, txBusyTmp : std_logic;-- FSM to avoid having the previous FSM dependend on a variable clock (clock skews pb)type stateClk is (waitClkTX, clkTXevent, waitReleaseClkTX);signal currentstateClk, futurestateClk: stateClk;signal clkTXbuf : std_logic;-- Various sigssignal sendPreamble, sendCounter, sendFIFO,sendCRC, txSigTmp, counterSig, loadRegPayload :std_logic;signal shiftReg1, shiftReg2 : std_logic;-- Preamble generation signalssignal preambTX:std_logic;begin-- ############################################-- main FSM process ; determine what it's doing-- ############################################process (currentstate, regH1, regH2, readFIFOtxOK, txStart, counter, octetCounter, lengthTX, txCounter)begin-- default outputstxBusyTmp