Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

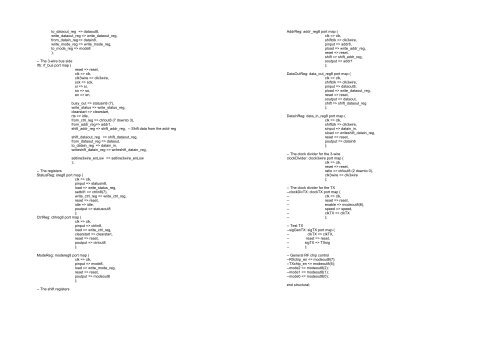

to_dataout_reg => dataout8,write_dataout_reg => write_dataout_reg,from_datain_reg => datain8,write_mode_reg => write_mode_reg,to_mode_reg => mode8);-- The 3-wire bus siderfb: rf_bus port map (reset => reset,clk => clk,clk3wire => clk3wire,sck => sck,si => si,so => so,en => en,busy_out => statusin8 (7),write_status => write_status_reg,clearstart => clearstart,rts => idle,from_ctrl_reg => ctrlout8 (7 downto 3),from_addr_reg => addr1,shift_addr_reg => shift_addr_reg, -- Shift data from the addr regshift_dataout_reg => shift_dataout_reg,from_dataout_reg => dataout,to_datain_reg => datain_in,writeshift_datain_reg => writeshift_datain_reg,setline3wire_enLow => setline3wire_enLow);-- The registersStatusReg: sreg8 port map (clk => clk,pinput => statusin8,load => write_status_reg,setbit1 => ctrlin8(7),write_ctrl_reg => write_ctrl_reg,reset => reset,idle => idle,poutput => statusout8);CtrlReg: ctrlreg8 port map (clk => clk,pinput => ctrlin8,load => write_ctrl_reg,clearstart => clearstart,reset => reset,poutput => ctrlout8);ModeReg: modereg8 port map (clk => clk,pinput => mode8,load => write_mode_reg,reset => reset,poutput => modeout8);-- The shift registersAddrReg: addr_reg8 port map (clk => clk,shiftclk => clk3wire,pinput => addr8,pload => write_addr_reg,reset => reset,shift => shift_addr_reg,soutput => addr1);DataOutReg: data_out_reg8 port map (clk => clk,shiftclk => clk3wire,pinput => dataout8,pload => write_dataout_reg,reset => reset,soutput => dataout,shift => shift_dataout_reg);DataInReg: data_in_reg8 port map (clk => clk,shiftclk => clk3wire,sinput => datain_in,sload => writeshift_datain_reg,reset => reset,poutput => datain8);-- The clock divider <strong>for</strong> the 3-wireclockDivider: clock3wire port map (clk => clk,reset => reset,ratio => ctrlout8 (2 downto 0),clk3wire => clk3wire);-- The clock divider <strong>for</strong> the TX--clockDivTX: clockTX port map (-- clk => clk,-- reset => reset,-- enable => modeout8(6),-- speed => speed,-- clkTX => clkTX-- );-- Test TX--sigGenTX: sigTX port map (-- clkTX => clkTX,-- reset => reset,-- sigTX => TXsig-- );-- General RF chip control--RXchip_en