Xcell Journal: The authoritative journal for programmable ... - Xilinx

Xcell Journal: The authoritative journal for programmable ... - Xilinx

Xcell Journal: The authoritative journal for programmable ... - Xilinx

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

GSRD Overview<br />

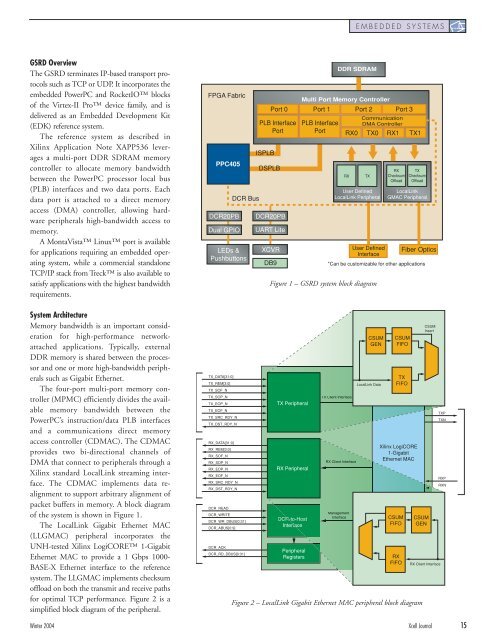

<strong>The</strong> GSRD terminates IP-based transport protocols<br />

such as TCP or UDP. It incorporates the<br />

embedded PowerPC and RocketIO blocks<br />

of the Virtex-II Pro device family, and is<br />

delivered as an Embedded Development Kit<br />

(EDK) reference system.<br />

<strong>The</strong> reference system as described in<br />

<strong>Xilinx</strong> Application Note XAPP536 leverages<br />

a multi-port DDR SDRAM memory<br />

controller to allocate memory bandwidth<br />

between the PowerPC processor local bus<br />

(PLB) interfaces and two data ports. Each<br />

data port is attached to a direct memory<br />

access (DMA) controller, allowing hardware<br />

peripherals high-bandwidth access to<br />

memory.<br />

A MontaVista Linux port is available<br />

<strong>for</strong> applications requiring an embedded operating<br />

system, while a commercial standalone<br />

TCP/IP stack from Treck is also available to<br />

satisfy applications with the highest bandwidth<br />

requirements.<br />

System Architecture<br />

Memory bandwidth is an important consideration<br />

<strong>for</strong> high-per<strong>for</strong>mance networkattached<br />

applications. Typically, external<br />

DDR memory is shared between the processor<br />

and one or more high-bandwidth peripherals<br />

such as Gigabit Ethernet.<br />

<strong>The</strong> four-port multi-port memory controller<br />

(MPMC) efficiently divides the available<br />

memory bandwidth between the<br />

PowerPC’s instruction/data PLB interfaces<br />

and a communications direct memory<br />

access controller (CDMAC). <strong>The</strong> CDMAC<br />

provides two bi-directional channels of<br />

DMA that connect to peripherals through a<br />

<strong>Xilinx</strong> standard LocalLink streaming interface.<br />

<strong>The</strong> CDMAC implements data realignment<br />

to support arbitrary alignment of<br />

packet buffers in memory. A block diagram<br />

of the system is shown in Figure 1.<br />

<strong>The</strong> LocalLink Gigabit Ethernet MAC<br />

(LLGMAC) peripheral incorporates the<br />

UNH-tested <strong>Xilinx</strong> LogiCORE 1-Gigabit<br />

Ethernet MAC to provide a 1 Gbps 1000-<br />

BASE-X Ethernet interface to the reference<br />

system. <strong>The</strong> LLGMAC implements checksum<br />

offload on both the transmit and receive paths<br />

<strong>for</strong> optimal TCP per<strong>for</strong>mance. Figure 2 is a<br />

simplified block diagram of the peripheral.<br />

FPGA Fabric<br />

PPC405<br />

DCR20PB<br />

Dual GPIO<br />

LEDs &<br />

Pushbuttons<br />

TX_DATA[31:0]<br />

TX_REM[3:0]<br />

TX_SOF_N<br />

TX_SOP_N<br />

TX_EOP_N<br />

TX_EOF_N<br />

TX_SRC_RDY_N<br />

TX_DST_RDY_N<br />

RX_DATA[31:0]<br />

RX_REM[3:0]<br />

RX_SOF_N<br />

RX_SOP_N<br />

RX_EOP_N<br />

RX_EOF_N<br />

RX_SRC_RDY_N<br />

RX_DST_RDY_N<br />

DCR_READ<br />

DCR_WRITE<br />

DCR Bus<br />

DCR_WR_DBUS[0:31]<br />

DCR_ABUS[0:9]<br />

DCR_ACK<br />

DCR_RD_DBUS[0:31]<br />

DCR20PB<br />

UART Lite<br />

Winter 2004 <strong>Xcell</strong> <strong>Journal</strong> 15<br />

ISPLB<br />

DSPLB<br />

Port 0 Port 1 Port 2 Port 3<br />

PLB Interface<br />

Port<br />

XCVR<br />

DB9<br />

Multi Port Memory Controller<br />

PLB Interface<br />

Port<br />

EMBEDDED SYSTEMS<br />

DDR SDRAM<br />

Communication<br />

DMA Controller<br />

RX0 TX0 RX1 TX1<br />

RX TX<br />

User Defined<br />

LocalLink Peripheral<br />

User Defined<br />

Interface<br />

RX<br />

Checksum<br />

Offload<br />

TX<br />

Checksum<br />

Offload<br />

LocalLink<br />

GMAC Peripheral<br />

Fiber Optics<br />

*Can be customizable <strong>for</strong> other applications<br />

Figure 1 – GSRD system block diagram<br />

TX Peripheral<br />

RX Peripheral<br />

R<br />

fa<br />

Peripheral<br />

Registers<br />

CSUM<br />

GEN<br />

LocalLink Data<br />

CSUM<br />

FIFO<br />

TX<br />

FIFO<br />

<strong>Xilinx</strong> LogiCORE<br />

1-Gigabit<br />

Ethernet MAC<br />

CSUM<br />

FIFO<br />

RX<br />

FIFO<br />

Figure 2 – LocalLink Gigabit Ethernet MAC peripheral block diagram<br />

CSUM<br />

GEN<br />

CSUM<br />

Insert<br />

RX Client Interface<br />

TXP<br />

TXN<br />

RXP<br />

RXN