Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Numonyx <strong>Wireless</strong> <strong>Flash</strong> <strong>Memory</strong> (<strong>W30</strong>)<br />

Table 19: Bus Cycle Definitions<br />

Operation Command<br />

Protection<br />

Bus<br />

Cycles<br />

Protection Program 2 Write PA C0h Write PA PD<br />

Lock Protection Program 2 Write LPA C0h Write LPA FFFDh<br />

Configuration<br />

Notes:<br />

Set Configuration<br />

Register<br />

2 Write CD 60h Write CD 03h<br />

1. First-cycle command addresses must be the same as the target address of the operation. Examples:<br />

—The first-cycle address for the Read Identifier command must be the same as the Identification code address (IA).<br />

—The first-cycle address for the Word Program command must be the same as the word address (WA) to be<br />

programmed.<br />

—The first-cycle address for the Erase/Program Suspend command must be the same as the address within the block<br />

to be suspended.<br />

XX= Any valid address within the flash device.<br />

IA= Identification code address.<br />

BA= Block Address. Any address within a specific block.<br />

LPA= The Lock Protection Address is obtained from the CFI (through the Read Query command). The <strong>W30</strong> flash<br />

memory device family LPA is at 0080h.<br />

PA= User programmable 4-word protection address.<br />

PnA= Any address within a specific partition.<br />

PBA= Partition Base Address. The first address of a particular partition.<br />

QA= Query code address.<br />

WA= Word address of memory location to be written.<br />

2. SRD= Status register data.<br />

WD= Data to be written at location WA.<br />

IC= Identifier code data.<br />

PD= User programmable 4-word protection data.<br />

QD= Query code data on D[7:0].<br />

CD= Configuration register code data presented on flash device addresses A[15:0]. A[MAX:16] address bits can<br />

select any partition. See Table 27, “Read Configuration Register Definitions” on page 79 for<br />

configuration<br />

register bits descriptions.<br />

3. Do not use commands other than those shown above. Other commands are reserved by Numonyx for future flash<br />

device implementations.<br />

9.3 Command Sequencing<br />

First Bus Cycle Second Bus Cycle<br />

Oper Addr 1<br />

Data 2,3<br />

Oper Addr 1<br />

Data 2,3<br />

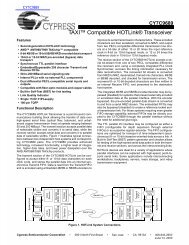

When issuing a 2-cycle write sequence to the flash device, a read operation can occur<br />

between the two write cycles. The setup phase of a 2-cycle write sequence places the<br />

addressed partition into read-status mode, so if the same partition is read before the<br />

second confirm write cycle is issued, status register data is returned. Reads from other<br />

partitions, however, can return actual array data, if the addressed partition is already in<br />

read-array mode. Figure 25 and Figure 26 illustrate these two conditions.<br />

Figure 25: Normal Write and Read Cycles<br />

Address [A]<br />

WE# [W]<br />

OE# [G]<br />

Data [Q]<br />

Partition A Partition A Partition A<br />

20h D0h FFh<br />

Block Erase Setup Block Erase Conf irm Read Array<br />

November 2007 Datasheet<br />

Order Number: 290702-13 53