Intel Server Board S1200BT - PROconsult Data A/S

Intel Server Board S1200BT - PROconsult Data A/S

Intel Server Board S1200BT - PROconsult Data A/S

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Platform Management<br />

<strong>Intel</strong>® <strong>Server</strong> <strong>Board</strong> <strong>S1200BT</strong> TPS<br />

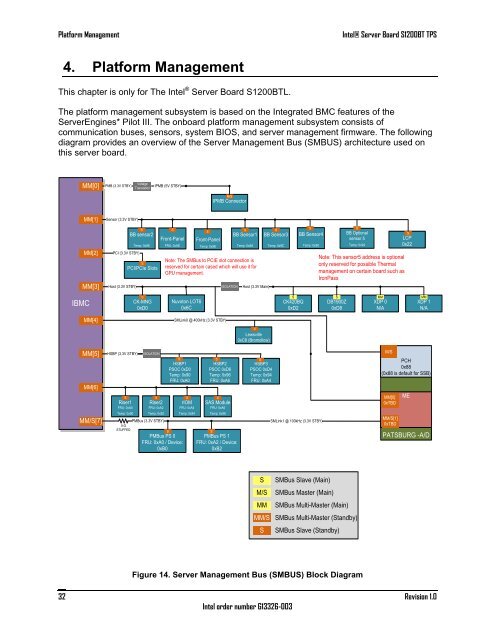

4. Platform Management<br />

This chapter is only for The <strong>Intel</strong> ® <strong>Server</strong> <strong>Board</strong> <strong>S1200BT</strong>L.<br />

The platform management subsystem is based on the Integrated BMC features of the<br />

<strong>Server</strong>Engines* Pilot III. The onboard platform management subsystem consists of<br />

communication buses, sensors, system BIOS, and server management firmware. The following<br />

diagram provides an overview of the <strong>Server</strong> Management Bus (SMBUS) architecture used on<br />

this server board.<br />

MM[0]<br />

IPMB (3.3V STBY)<br />

Voltage<br />

Translation<br />

IPMB (5V STBY)<br />

M/S<br />

IPMB Connector<br />

MM[1]<br />

MM[2]<br />

MM[3]<br />

Sensor (3.3V STBY)<br />

PCI (3.3V STBY)<br />

Host (3.3V STBY)<br />

S<br />

BB sensor2<br />

Temp: 0x98<br />

S<br />

PCI/PCIe Slots<br />

S<br />

Front-Panel<br />

FRU: 0xAE<br />

S<br />

Front-Panel<br />

Temp: 0x9E<br />

ISOLATION<br />

BB Sensor1<br />

Temp: 0x9A<br />

Note: The SMBus to PCIE slot connection is<br />

reserved for certain cased which will use it for<br />

GPU management.<br />

S<br />

Host (3.3V Main)<br />

S<br />

BB Sensor3<br />

Temp: 0x9C<br />

S<br />

BB Sensor4<br />

Temp: 0x96<br />

S<br />

BB Optional<br />

sensor 5<br />

Temp: 0x94<br />

Note: This sensor5 address is optional<br />

only reserved for possible Thermal<br />

management on certain board such as<br />

IronPass<br />

S<br />

LCP<br />

0x22<br />

IBMC<br />

S<br />

CK-MNG<br />

0xD0<br />

Nuvoton LOT6<br />

0x6C<br />

S<br />

CK420BQ<br />

0xD2<br />

S<br />

DB1900Z<br />

0xD8<br />

MM<br />

XDP 0<br />

N/A<br />

MM<br />

XDP 1<br />

N/A<br />

MM[4]<br />

SMLink0 @ 400kHz (3.3V STBY)<br />

MM[5]<br />

MM[6]<br />

MM/S[7]<br />

HSBP (3.3V STBY)<br />

S<br />

Riser1<br />

FRU: 0xA0<br />

Temp: 0x90<br />

0-Ω<br />

STUFFED<br />

ISOLATION<br />

S<br />

Riser2<br />

FRU: 0xA2<br />

Temp: 0x92<br />

PMBus (3.3V STBY)<br />

HSBP1<br />

PSOC 0xD0<br />

Temp: 0x90<br />

FRU: 0xA0<br />

S<br />

PMBus PS 0<br />

FRU: 0xA0 / Device:<br />

0xB0<br />

S<br />

rIOM<br />

FRU: 0xA4<br />

Temp: 0x94<br />

S<br />

SAS Module<br />

FRU: 0xA6<br />

Temp: 0x96<br />

S<br />

PMBus PS 1<br />

FRU: 0xA2 / Device:<br />

0xB2<br />

S<br />

Lewsville<br />

0xC8 (Bromollow)<br />

S S S<br />

HSBP2<br />

PSOC 0xD6<br />

Temp: 0x96<br />

FRU: 0xA6<br />

HSBP3<br />

PSOC 0xD4<br />

Temp: 0x94<br />

FRU: 0xA4<br />

SMLink1 @ 100kHz (3.3V STBY)<br />

M/S<br />

PCH<br />

0x88<br />

(0x88 is default for SSB)<br />

MM[0]<br />

0xTBD<br />

MM/S[1]<br />

0xTBD<br />

ME<br />

PATSBURG -A/D<br />

S<br />

M/S<br />

MM<br />

MM/S<br />

S<br />

SMBus Slave (Main)<br />

SMBus Master (Main)<br />

SMBus Multi-Master (Main)<br />

SMBus Multi-Master (Standby)<br />

SMBus Slave (Standby)<br />

Figure 14. <strong>Server</strong> Management Bus (SMBUS) Block Diagram<br />

32<br />

<strong>Intel</strong> order number G13326-003<br />

Revision 1.0