PIC16F84A 18-pin Enhanced Flash/EEPROM 8-Bit MCU Data Sheet

PIC16F84A 18-pin Enhanced Flash/EEPROM 8-Bit MCU Data Sheet

PIC16F84A 18-pin Enhanced Flash/EEPROM 8-Bit MCU Data Sheet

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

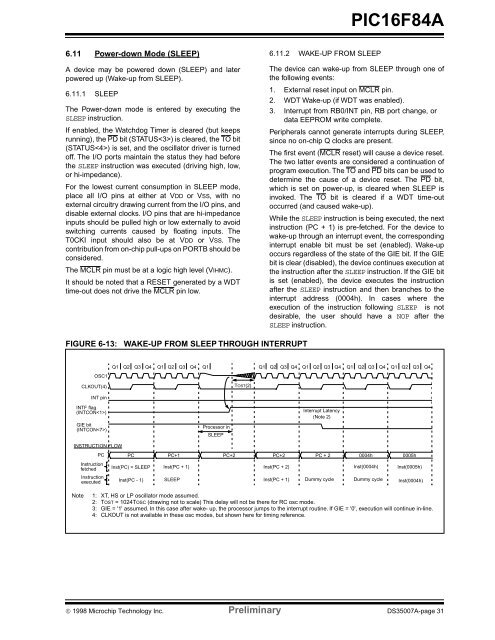

<strong>PIC16F84A</strong>6.11 Power-down Mode (SLEEP)A device may be powered down (SLEEP) and laterpowered up (Wake-up from SLEEP).6.11.1 SLEEPThe Power-down mode is entered by executing theSLEEP instruction.If enabled, the Watchdog Timer is cleared (but keepsrunning), the PD bit (STATUS) is cleared, the TO bit(STATUS) is set, and the oscillator driver is turnedoff. The I/O ports maintain the status they had beforethe SLEEP instruction was executed (driving high, low,or hi-impedance).For the lowest current consumption in SLEEP mode,place all I/O <strong>pin</strong>s at either at VDD or VSS, with noexternal circuitry drawing current from the I/O <strong>pin</strong>s, anddisable external clocks. I/O <strong>pin</strong>s that are hi-impedanceinputs should be pulled high or low externally to avoidswitching currents caused by floating inputs. TheT0CKI input should also be at VDD or VSS. Thecontribution from on-chip pull-ups on PORTB should beconsidered.The MCLR <strong>pin</strong> must be at a logic high level (VIHMC).It should be noted that a RESET generated by a WDTtime-out does not drive the MCLR <strong>pin</strong> low.6.11.2 WAKE-UP FROM SLEEPThe device can wake-up from SLEEP through one ofthe following events:1. External reset input on MCLR <strong>pin</strong>.2. WDT Wake-up (if WDT was enabled).3. Interrupt from RB0/INT <strong>pin</strong>, RB port change, ordata <strong>EEPROM</strong> write complete.Peripherals cannot generate interrupts during SLEEP,since no on-chip Q clocks are present.The first event (MCLR reset) will cause a device reset.The two latter events are considered a continuation ofprogram execution. The TO and PD bits can be used todetermine the cause of a device reset. The PD bit,which is set on power-up, is cleared when SLEEP isinvoked. The TO bit is cleared if a WDT time-outoccurred (and caused wake-up).While the SLEEP instruction is being executed, the nextinstruction (PC + 1) is pre-fetched. For the device towake-up through an interrupt event, the correspondinginterrupt enable bit must be set (enabled). Wake-upoccurs regardless of the state of the GIE bit. If the GIEbit is clear (disabled), the device continues execution atthe instruction after the SLEEP instruction. If the GIE bitis set (enabled), the device executes the instructionafter the SLEEP instruction and then branches to theinterrupt address (0004h). In cases where theexecution of the instruction following SLEEP is notdesirable, the user should have a NOP after theSLEEP instruction.FIGURE 6-13:WAKE-UP FROM SLEEP THROUGH INTERRUPTOSC1CLKOUT(4)Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4TOST(2)INT <strong>pin</strong>INTF flag(INTCON)GIE bit(INTCON)Processor inSLEEPInterrupt Latency(Note 2)INSTRUCTION FLOWPCInstructionfetchedInstructionexecutedPC PC+1 PC+2Inst(PC) = SLEEPInst(PC - 1)Inst(PC + 1)SLEEPPC+2Inst(PC + 2)Inst(PC + 1)PC + 2 0004h 0005hInst(0004h) Inst(0005h)Dummy cycle Dummy cycle Inst(0004h)Note1: XT, HS or LP oscillator mode assumed.2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.4: CLKOUT is not available in these osc modes, but shown here for timing reference.© 1998 Microchip Technology Inc. Preliminary DS35007A-page 31