PIC16F84A 18-pin Enhanced Flash/EEPROM 8-Bit MCU Data Sheet

PIC16F84A 18-pin Enhanced Flash/EEPROM 8-Bit MCU Data Sheet

PIC16F84A 18-pin Enhanced Flash/EEPROM 8-Bit MCU Data Sheet

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

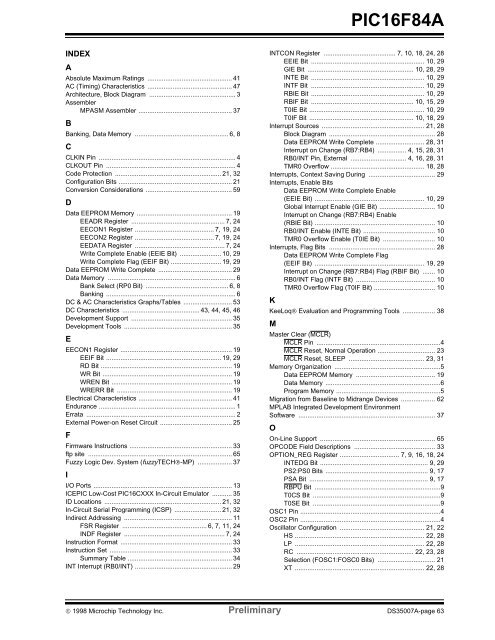

<strong>PIC16F84A</strong>INDEXAAbsolute Maximum Ratings ............................................... 41AC (Timing) Characteristics ............................................... 47Architecture, Block Diagram ................................................ 3AssemblerMPASM Assembler .................................................... 37BBanking, <strong>Data</strong> Memory .................................................... 6, 8CCLKIN Pin ............................................................................ 4CLKOUT Pin ........................................................................ 4Code Protection ........................................................... 21, 32Configuration <strong>Bit</strong>s ............................................................... 21Conversion Considerations ................................................ 59D<strong>Data</strong> <strong>EEPROM</strong> Memory ..................................................... 19EEADR Register .................................................... 7, 24EECON1 Register ............................................ 7, 19, 24EECON2 Register ............................................ 7, 19, 24EEDATA Register .................................................. 7, 24Write Complete Enable (EEIE <strong>Bit</strong>) ....................... 10, 29Write Complete Flag (EEIF <strong>Bit</strong>) ............................ 19, 29<strong>Data</strong> <strong>EEPROM</strong> Write Complete ......................................... 29<strong>Data</strong> Memory ....................................................................... 6Bank Select (RP0 <strong>Bit</strong>) .............................................. 6, 8Banking ........................................................................ 6DC & AC Characteristics Graphs/Tables ........................... 53DC Characteristics ........................................... 43, 44, 45, 46Development Support ........................................................ 35Development Tools ............................................................ 35EEECON1 Register .............................................................. 19EEIF <strong>Bit</strong> ................................................................ 19, 29RD <strong>Bit</strong> ......................................................................... 19WR <strong>Bit</strong> ........................................................................ 19WREN <strong>Bit</strong> ................................................................... 19WRERR <strong>Bit</strong> ................................................................ 19Electrical Characteristics .................................................... 41Endurance ............................................................................ 1Errata ................................................................................... 2External Power-on Reset Circuit ........................................ 25FFirmware Instructions ......................................................... 33ftp site ................................................................................ 65Fuzzy Logic Dev. System (fuzzyTECH®-MP) ................... 37II/O Ports ............................................................................. 13ICEPIC Low-Cost PIC16CXXX In-Circuit Emulator ........... 35ID Locations ................................................................. 21, 32In-Circuit Serial Programming (ICSP) .......................... 21, 32Indirect Addressing ............................................................ 11FSR Register ............................................... 6, 7, 11, 24INDF Register ........................................................ 7, 24Instruction Format .............................................................. 33Instruction Set .................................................................... 33Summary Table .......................................................... 34INT Interrupt (RB0/INT) ...................................................... 29INTCON Register ........................................ 7, 10, <strong>18</strong>, 24, 28EEIE <strong>Bit</strong> ............................................................... 10, 29GIE <strong>Bit</strong> ........................................................... 10, 28, 29INTE <strong>Bit</strong> ............................................................... 10, 29INTF <strong>Bit</strong> ............................................................... 10, 29RBIE <strong>Bit</strong> ............................................................... 10, 29RBIF <strong>Bit</strong> ......................................................... 10, 15, 29T0IE <strong>Bit</strong> ................................................................ 10, 29T0IF <strong>Bit</strong> .......................................................... 10, <strong>18</strong>, 29Interrupt Sources ......................................................... 21, 28Block Diagram ........................................................... 28<strong>Data</strong> <strong>EEPROM</strong> Write Complete ........................... 28, 31Interrupt on Change (RB7:RB4) ................ 4, 15, 28, 31RB0/INT Pin, External ............................... 4, 16, 28, 31TMR0 Overflow .................................................... <strong>18</strong>, 28Interrupts, Context Saving During ..................................... 29Interrupts, Enable <strong>Bit</strong>s<strong>Data</strong> <strong>EEPROM</strong> Write Complete Enable(EEIE <strong>Bit</strong>) ............................................................. 10, 29Global Interrupt Enable (GIE <strong>Bit</strong>) ............................... 10Interrupt on Change (RB7:RB4) Enable(RBIE <strong>Bit</strong>) ................................................................... 10RB0/INT Enable (INTE <strong>Bit</strong>) ........................................ 10TMR0 Overflow Enable (T0IE <strong>Bit</strong>) ............................. 10Interrupts, Flag <strong>Bit</strong>s ........................................................... 28<strong>Data</strong> <strong>EEPROM</strong> Write Complete Flag(EEIF <strong>Bit</strong>) ............................................................. 19, 29Interrupt on Change (RB7:RB4) Flag (RBIF <strong>Bit</strong>) ....... 10RB0/INT Flag (INTF <strong>Bit</strong>) ............................................ 10TMR0 Overflow Flag (T0IF <strong>Bit</strong>) .................................. 10KKeeLoq® Evaluation and Programming Tools .................. 38MMaster Clear (MCLR)MCLR Pin .....................................................................4MCLR Reset, Normal Operation ................................ 23MCLR Reset, SLEEP .......................................... 23, 31Memory Organization ...........................................................5<strong>Data</strong> <strong>EEPROM</strong> Memory ............................................ 19<strong>Data</strong> Memory ................................................................6Program Memory ..........................................................5Migration from Baseline to Midrange Devices ................... 62MPLAB Integrated Development EnvironmentSoftware ............................................................................ 37OOn-Line Support ................................................................ 65OPCODE Field Descriptions ............................................. 33OPTION_REG Register ................................. 7, 9, 16, <strong>18</strong>, 24INTEDG <strong>Bit</strong> ............................................................ 9, 29PS2:PS0 <strong>Bit</strong>s ......................................................... 9, 17PSA <strong>Bit</strong> .................................................................. 9, 17RBPU <strong>Bit</strong> ......................................................................9T0CS <strong>Bit</strong> .......................................................................9T0SE <strong>Bit</strong> .......................................................................9OSC1 Pin ..............................................................................4OSC2 Pin ..............................................................................4Oscillator Configuration ............................................... 21, 22HS ........................................................................ 22, 28LP ........................................................................ 22, 28RC ................................................................. 22, 23, 28Selection (FOSC1:FOSC0 <strong>Bit</strong>s) ................................ 21XT ........................................................................ 22, 28© 1998 Microchip Technology Inc. Preliminary DS35007A-page 63