UltraScale Architecture Memory Resources

ug573-ultrascale-memory-resources

ug573-ultrascale-memory-resources

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 1: Block RAM <strong>Resources</strong><br />

Inverting Control Pins<br />

For each port, the eight control pins (CLK, EN, RSTREG, and RSTRAM) each have an<br />

individual inversion option. EN, RSTREG, and RSTRAM control signals can be configured as<br />

active-High or Low, and the clock can be active on a rising or falling edge (active-High on<br />

rising edge by default), without requiring other logic resources.<br />

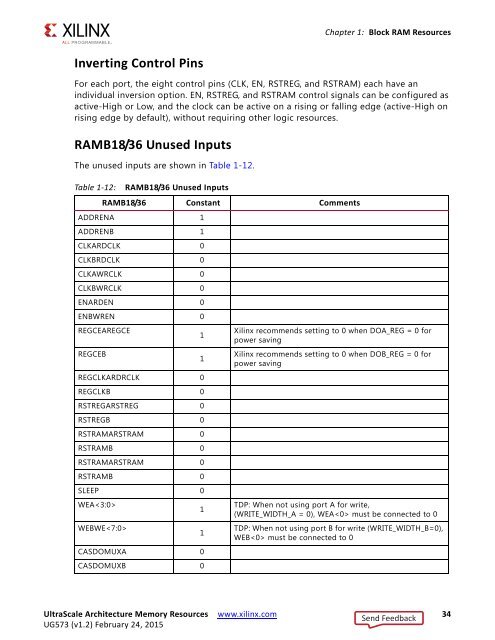

RAMB18/36 Unused Inputs<br />

The unused inputs are shown in Table 1-12.<br />

Table 1-12:<br />

RAMB18/36 Unused Inputs<br />

RAMB18/36 Constant Comments<br />

ADDRENA 1<br />

ADDRENB 1<br />

CLKARDCLK 0<br />

CLKBRDCLK 0<br />

CLKAWRCLK 0<br />

CLKBWRCLK 0<br />

ENARDEN 0<br />

ENBWREN 0<br />

REGCEAREGCE<br />

REGCEB<br />

REGCLKARDRCLK 0<br />

REGCLKB 0<br />

RSTREGARSTREG 0<br />

RSTREGB 0<br />

RSTRAMARSTRAM 0<br />

RSTRAMB 0<br />

RSTRAMARSTRAM 0<br />

RSTRAMB 0<br />

SLEEP 0<br />

WEA<br />

WEBWE<br />

CASDOMUXA 0<br />

CASDOMUXB 0<br />

1<br />

1<br />

1<br />

1<br />

Xilinx recommends setting to 0 when DOA_REG = 0 for<br />

power saving<br />

Xilinx recommends setting to 0 when DOB_REG = 0 for<br />

power saving<br />

TDP: When not using port A for write,<br />

(WRITE_WIDTH_A = 0), WEA must be connected to 0<br />

TDP: When not using port B for write (WRITE_WIDTH_B=0),<br />

WEB must be connected to 0<br />

<strong>UltraScale</strong> <strong>Architecture</strong> <strong>Memory</strong> <strong>Resources</strong> www.xilinx.com<br />

Send Feedback<br />

34<br />

UG573 (v1.2) February 24, 2015