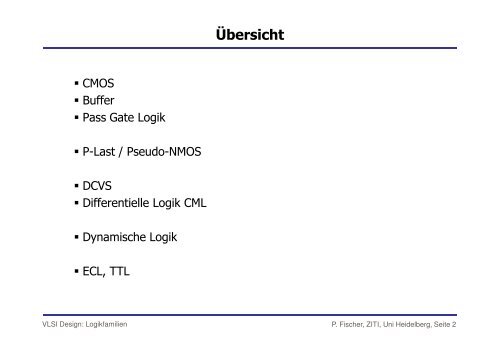

- Seite 1: VLSI Design: Logikfamilien Logikfam

- Seite 5 und 6: V GS VDD S D Warum PMOS für pullup

- Seite 7 und 8: � Schaltbild zur Simulation der n

- Seite 9 und 10: CMOS Inverter Transferkennlinie �

- Seite 11 und 12: � Für den NMOS ist V GS = V in,

- Seite 13 und 14: Transientenanalyse � Simulation e

- Seite 15 und 16: Sensitivität der Schwelle � Trä

- Seite 17 und 18: � Hiermit ist meist Durchlaufzeit

- Seite 19 und 20: � PSPICE mit nmos25, pmos25. �

- Seite 21 und 22: � Aus Rabey, 1.2µm Technologie,

- Seite 23 und 24: Einfluß der Anstiegszeit des Einga

- Seite 25 und 26: Leistungsverbrauch (2) 2. Dynamisch

- Seite 27 und 28: A B CMOS NAND / NOR NAND2 A B F NOR

- Seite 29 und 30: a b c a b c a b f komplexere Gatter

- Seite 31 und 32: Stick Diagramm � Um die Topologie

- Seite 33 und 34: a b c Zwei unterschiedliche Stick L

- Seite 35 und 36: a b a c c a VLSI Design: Logikfamil

- Seite 37 und 38: Transistorgrößen in MOS Gattern

- Seite 39 und 40: Ideale Transistorgröße in komplex

- Seite 41 und 42: t p im NAND als Funktion des Fan-In

- Seite 43 und 44: A B A B A B VLSI Design: Logikfamil

- Seite 45 und 46: Volladdierer � Der Carry-Pfad mu

- Seite 47 und 48: Optimierter Volladdierer (invertier

- Seite 49 und 50: BUFFER VLSI Design: Logikfamilien P

- Seite 51 und 52: Inverterkette als Buffer � Lösun

- Seite 53 und 54:

RC vs. t pd � Ein RC Glied erzeug

- Seite 55 und 56:

Beispiel 0.18µm Technologie � Be

- Seite 57 und 58:

NMOS LOGIK VLSI Design: Logikfamili

- Seite 59 und 60:

Querstrom PMOS VLSI Design: Logikfa

- Seite 61 und 62:

Berechnung V OL � Berechnung der

- Seite 63 und 64:

P-Last NOR6 � Hier mit sehr lange

- Seite 65 und 66:

Pseudo NMOS mit Adaptiver Last �

- Seite 67 und 68:

Pass-Transistor Logik: Nur NMOS Sch

- Seite 69 und 70:

Einschub: Widerstand eines MOS �

- Seite 71 und 72:

Problem bei niedrigen Versorgungssp

- Seite 73 und 74:

out A B A ⊕ B 0 0 0 0 1 1 1 0 1 1

- Seite 75 und 76:

Tri-State Ausgang � Die zwei in S

- Seite 77 und 78:

D !LD Latch mit Gated Invertern - S

- Seite 79 und 80:

Latch mit 'Keeper' � Die Speicher

- Seite 81 und 82:

'NMOS -Only' Transmission Gate Logi

- Seite 83 und 84:

DIFFERENTIELLE CMOS LOGIK VLSI Desi

- Seite 85 und 86:

DCVS Logik � DCVSL = differential

- Seite 87 und 88:

a ⊕ b DCVS XOR b b b b a a a ⊕

- Seite 89 und 90:

V DCVS Inverter � Simulation mit

- Seite 91 und 92:

Ähnlich JK-FF: Getaktetes SR - Fli

- Seite 93 und 94:

� CML = 'Current Mode Logik' CML

- Seite 95 und 96:

Q !Q !A A A !A !Q VLSI Design: Logi

- Seite 97 und 98:

DYNAMISCHE LOGIK VLSI Design: Logik

- Seite 99 und 100:

VLSI Design: Logikfamilien Beispiel

- Seite 101 und 102:

Vorteile: � Nur N+2 Transistoren

- Seite 103 und 104:

φ a b φ � Schwacher PMOS hält

- Seite 105 und 106:

Einfluß der Kapazitäten � Drain

- Seite 107 und 108:

φ in Problem: 'Clock Feedthrough'

- Seite 109 und 110:

� Füge einen Inverter hinter jed

- Seite 111 und 112:

� Abwechselnd N-Stufen und P-Stuf

- Seite 113 und 114:

Beispiel: breites UND Gatter (Adres

- Seite 115 und 116:

Beispiel: breites ODER (z.B. f. Mat

- Seite 117 und 118:

FLIPFLOPS IN DYNAMISCHER LOGIK VLSI

- Seite 119 und 120:

CK D Dynamisches Ein-Phasen-FF !CK

- Seite 121 und 122:

'Echtes' Ein-Phasen dynamisches LAT

- Seite 123 und 124:

TSPC - True Single Phase Clock Logi

- Seite 125 und 126:

Vergleich einiger Logikfamilien �

- Seite 127 und 128:

Messung: auf der 1mm Leitung und hi

- Seite 129 und 130:

Messung: auf der 1mm Leitung und hi

- Seite 131 und 132:

Die Simulation zeigt den Effekt �

- Seite 133 und 134:

Zentrales Element von ECL: das diff

- Seite 135 und 136:

ECL � ECL = 'Emitter Coupled Logi

- Seite 137 und 138:

ECL: Differenzverstärker und Emitt

- Seite 139 und 140:

Wired-OR in ECL � Mehrere Ausgän

- Seite 141 und 142:

Vorteile: � Statische Logik Zusam

- Seite 143 und 144:

Vorläufer: Diode-Transistor-Logik

- Seite 145 und 146:

TTL mit Totem-Pole Ausgang � Ausg

- Seite 147 und 148:

TTL Familien � Es gibt mehrerer v

- Seite 149 und 150:

� Bipolare Logiken (TTL, ECL) auf

- Seite 151 und 152:

� Sender hat NMOS Open-Drain Ausg

- Seite 153 und 154:

Ausblick: LVDS Treiber � Zur Erze

- Seite 155 und 156:

VLSI Design: Logikfamilien Vergleic

- Seite 157:

VLSI Design: Logikfamilien 'Glue Lo