Logikfamilien (4.2 MB)

Logikfamilien (4.2 MB)

Logikfamilien (4.2 MB)

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

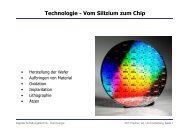

� β= K x W/L muß maximiert werden, daher L = L min<br />

Wahl der Transistorgrößen<br />

� Für die Wahl des Verhältnisses von β p/β n gibt es verschiedene Kriterien:<br />

- Maximaler Störabstand, also V T = VDD/2 ⇒ β p = β n<br />

- gleiche Anstiegs- und Abfallzeiten ⇒ β p = β n<br />

- Minimale mittlere Verzögerung ⇒ β p < β n (Kapazität durch PMOS kleiner halten!)<br />

� Zusammen mit den Technologiekonstanten K N und K P legt man so W P/W N fest<br />

� Der Absolutwert von W N hängt von der zu treibenden Last ab.<br />

Je größer die Last, desto größer sollten die Ws sein.<br />

Damit steigt aber auch die Eingangskapazität.<br />

� Bei sehr großen Lasten sollte man daher lieber 'minimale' Inverter/Gatter benutzen und Buffer einfügen<br />

(s. später)<br />

VLSI Design: <strong>Logikfamilien</strong><br />

P. Fischer, ZITI, Uni Heidelberg, Seite 26