Logikfamilien (4.2 MB)

Logikfamilien (4.2 MB)

Logikfamilien (4.2 MB)

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

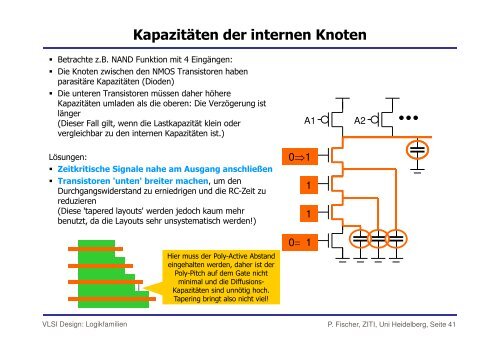

Kapazitäten der internen Knoten<br />

� Betrachte z.B. NAND Funktion mit 4 Eingängen:<br />

� Die Knoten zwischen den NMOS Transistoren haben<br />

parasitäre Kapazitäten (Dioden)<br />

� Die unteren Transistoren müssen daher höhere<br />

Kapazitäten umladen als die oberen: Die Verzögerung ist<br />

länger<br />

(Dieser Fall gilt, wenn die Lastkapazität klein oder<br />

vergleichbar zu den internen Kapazitäten ist.)<br />

Lösungen:<br />

� Zeitkritische Signale nahe am Ausgang anschließen<br />

� Transistoren 'unten' breiter machen, um den<br />

Durchgangswiderstand zu erniedrigen und die RC-Zeit zu<br />

reduzieren<br />

(Diese 'tapered layouts' werden jedoch kaum mehr<br />

benutzt, da die Layouts sehr unsystematisch werden!)<br />

VLSI Design: <strong>Logikfamilien</strong><br />

Hier muss der Poly-Active Abstand<br />

eingehalten werden, daher ist der<br />

Poly-Pitch auf dem Gate nicht<br />

minimal und die Diffusions-<br />

Kapazitäten sind unnötig hoch.<br />

Tapering bringt also nicht viel!<br />

0⇒1 A4 1<br />

A1 A2<br />

A3<br />

1<br />

A2<br />

1<br />

0⇒11<br />

A1<br />

P. Fischer, ZITI, Uni Heidelberg, Seite 41