Logikfamilien (4.2 MB)

Logikfamilien (4.2 MB)

Logikfamilien (4.2 MB)

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

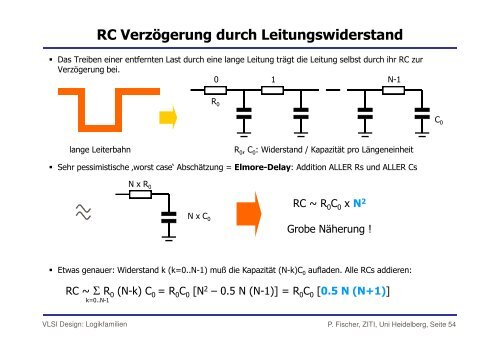

RC Verzögerung durch Leitungswiderstand<br />

� Das Treiben einer entfernten Last durch eine lange Leitung trägt die Leitung selbst durch ihr RC zur<br />

Verzögerung bei.<br />

0 1 N-1<br />

R 0<br />

lange Leiterbahn R 0, C 0: Widerstand / Kapazität pro Längeneinheit<br />

� Sehr pessimistische ‚worst case‘ Abschätzung = Elmore-Delay: Addition ALLER Rs und ALLER Cs<br />

N x R 0<br />

N x C 0<br />

RC ~ R 0C 0 x N 2<br />

Grobe Näherung !<br />

� Etwas genauer: Widerstand k (k=0..N-1) muß die Kapazität (N-k)C 0 aufladen. Alle RCs addieren:<br />

RC ~ Σ R 0 (N-k) C 0 = R 0C 0 [N 2 – 0.5 N (N-1)] = R 0C 0 [0.5 N (N+1)]<br />

k=0..N-1<br />

VLSI Design: <strong>Logikfamilien</strong><br />

C 0<br />

P. Fischer, ZITI, Uni Heidelberg, Seite 54