Logikfamilien (4.2 MB)

Logikfamilien (4.2 MB)

Logikfamilien (4.2 MB)

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

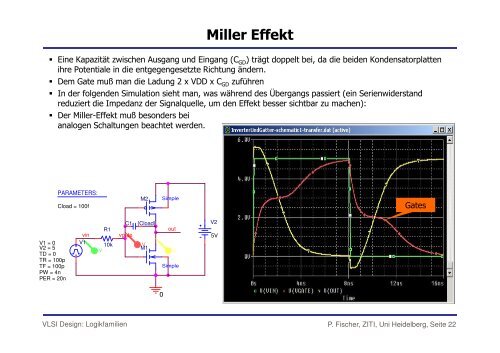

Miller Effekt<br />

� Eine Kapazität zwischen Ausgang und Eingang (C GD) trägt doppelt bei, da die beiden Kondensatorplatten<br />

ihre Potentiale in die entgegengesetzte Richtung ändern.<br />

� Dem Gate muß man die Ladung 2 x VDD x C GD zuführen<br />

� In der folgenden Simulation sieht man, was während des Übergangs passiert (ein Serienwiderstand<br />

reduziert die Impedanz der Signalquelle, um den Effekt besser sichtbar zu machen):<br />

� Der Miller-Effekt muß besonders bei<br />

analogen Schaltungen beachtet werden.<br />

V1 = 0<br />

V2 = 5<br />

TD = 0<br />

TR = 100p<br />

TF = 100p<br />

PW = 4n<br />

PER = 20n<br />

PARAMETERS:<br />

Cload = 100f<br />

vin<br />

V1<br />

R1<br />

10k<br />

V<br />

C1 {Cload}<br />

vgate<br />

VLSI Design: <strong>Logikfamilien</strong><br />

M2<br />

V<br />

M1<br />

0<br />

Simple<br />

out<br />

V<br />

Simple<br />

V2<br />

5V<br />

Gates<br />

P. Fischer, ZITI, Uni Heidelberg, Seite 22