Logikfamilien (4.2 MB)

Logikfamilien (4.2 MB)

Logikfamilien (4.2 MB)

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

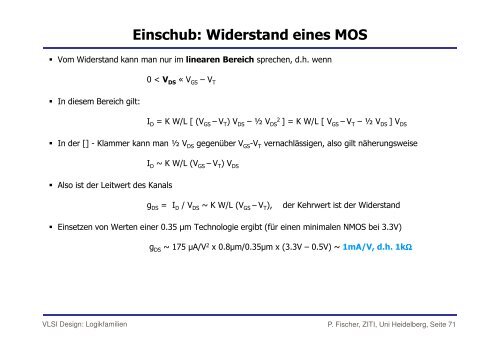

Einschub: Widerstand eines MOS<br />

� Vom Widerstand kann man nur im linearen Bereich sprechen, d.h. wenn<br />

� In diesem Bereich gilt:<br />

0 < V DS « V GS – V T<br />

I D = K W/L [ (V GS – V T) V DS – ½ V DS 2 ] = K W/L [ VGS – V T – ½ V DS ] V DS<br />

� In der [] - Klammer kann man ½ V DS gegenüber V GS-V T vernachlässigen, also gilt näherungsweise<br />

� Also ist der Leitwert des Kanals<br />

I D ~ K W/L (V GS – V T) V DS<br />

g DS = I D / V DS ~ K W/L (V GS – V T), der Kehrwert ist der Widerstand<br />

� Einsetzen von Werten einer 0.35 µm Technologie ergibt (für einen minimalen NMOS bei 3.3V)<br />

VLSI Design: <strong>Logikfamilien</strong><br />

g DS ~ 175 µA/V 2 x 0.8µm/0.35µm x (3.3V – 0.5V) ~ 1mA/V, d.h. 1kΩ<br />

P. Fischer, ZITI, Uni Heidelberg, Seite 71