Logikfamilien (4.2 MB)

Logikfamilien (4.2 MB)

Logikfamilien (4.2 MB)

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

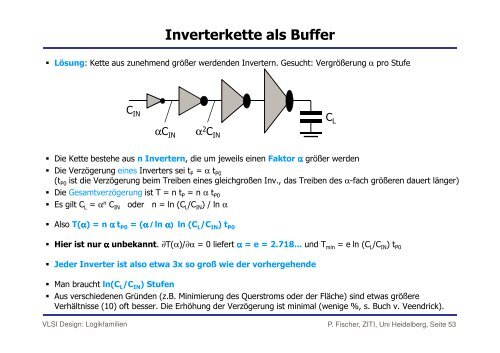

Inverterkette als Buffer<br />

� Lösung: Kette aus zunehmend größer werdenden Invertern. Gesucht: Vergrößerung α pro Stufe<br />

C IN<br />

αC IN<br />

α 2 C IN<br />

� Die Kette bestehe aus n Invertern, die um jeweils einen Faktor α größer werden<br />

� Die Verzögerung eines Inverters sei t P = α t P0<br />

(t (tP0 ist die Verzögerung beim Treiben eines gleichgroßen Inv., das Treiben des α-fach größeren dauert länger)<br />

� Die Gesamtverzögerung ist T = n t P = n α t P0<br />

� Es gilt C L = α n C IN oder n = ln (C L/C IN) / ln α<br />

� Also T(α) = n α tP0 = (α α / / ln α) ln (CL/CIN) tP0 � Hier ist nur α unbekannt. ∂T(α)/∂α = 0 liefert α = e = 2.718... und T min = e ln (C L/C IN) t P0<br />

� Jeder Inverter ist also etwa 3x so groß wie der vorhergehende<br />

� Man braucht ln(C L/C IN) Stufen<br />

� Aus verschiedenen Gründen (z.B. Minimierung des Querstroms oder der Fläche) sind etwas größere<br />

Verhältnisse (10) oft besser. Die Erhöhung der Verzögerung ist minimal (wenige %, s. Buch v. Veendrick).<br />

VLSI Design: <strong>Logikfamilien</strong><br />

C L<br />

P. Fischer, ZITI, Uni Heidelberg, Seite 53