Processor Local Bus Functional Model Toolkit User's Manual

Processor Local Bus Functional Model Toolkit User's Manual

Processor Local Bus Functional Model Toolkit User's Manual

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

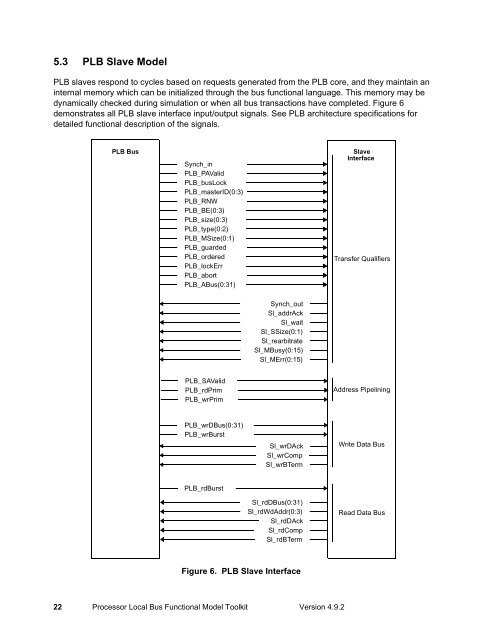

5.3 PLB Slave <strong>Model</strong><br />

PLB slaves respond to cycles based on requests generated from the PLB core, and they maintain an<br />

internal memory which can be initialized through the bus functional language. This memory may be<br />

dynamically checked during simulation or when all bus transactions have completed. Figure 6<br />

demonstrates all PLB slave interface input/output signals. See PLB architecture specifications for<br />

detailed functional description of the signals.<br />

PLB <strong>Bus</strong><br />

Synch_in<br />

PLB_PAValid<br />

PLB_busLock<br />

PLB_masterID(0:3)<br />

PLB_RNW<br />

PLB_BE(0:3)<br />

PLB_size(0:3)<br />

PLB_type(0:2)<br />

PLB_MSize(0:1)<br />

PLB_guarded<br />

PLB_ordered<br />

PLB_lockErr<br />

PLB_abort<br />

PLB_A<strong>Bus</strong>(0:31)<br />

PLB_SAValid<br />

PLB_rdPrim<br />

PLB_wrPrim<br />

PLB_wrD<strong>Bus</strong>(0:31)<br />

PLB_wrBurst<br />

PLB_rdBurst<br />

Synch_out<br />

Sl_addrAck<br />

Sl_wait<br />

Sl_SSize(0:1)<br />

Sl_rearbitrate<br />

Sl_M<strong>Bus</strong>y(0:15)<br />

Sl_MErr(0:15)<br />

Sl_wrDAck<br />

Sl_wrComp<br />

Sl_wrBTerm<br />

Sl_rdD<strong>Bus</strong>(0:31)<br />

Sl_rdWdAddr(0:3)<br />

Sl_rdDAck<br />

Sl_rdComp<br />

Sl_rdBTerm<br />

Figure 6. PLB Slave Interface<br />

22 <strong>Processor</strong> <strong>Local</strong> <strong>Bus</strong> <strong>Functional</strong> <strong>Model</strong> <strong>Toolkit</strong> Version 4.9.2<br />

Slave<br />

Interface<br />

Transfer Qualifiers<br />

Address Pipelining<br />

Write Data <strong>Bus</strong><br />

Read Data <strong>Bus</strong>