Processor Local Bus Functional Model Toolkit User's Manual

Processor Local Bus Functional Model Toolkit User's Manual

Processor Local Bus Functional Model Toolkit User's Manual

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

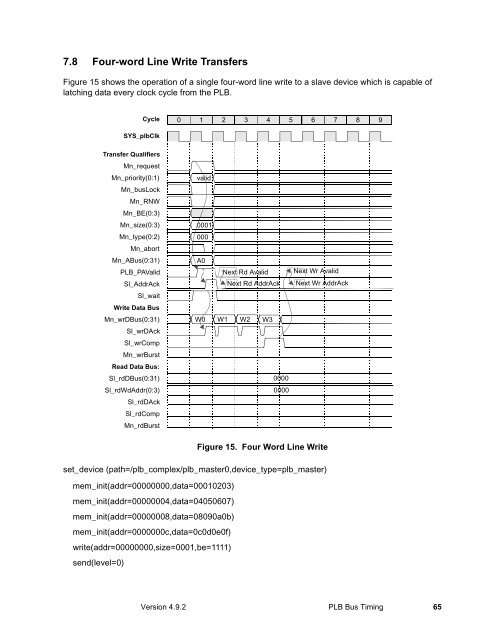

7.8 Four-word Line Write Transfers<br />

Figure 15 shows the operation of a single four-word line write to a slave device which is capable of<br />

latching data every clock cycle from the PLB.<br />

set_device (path=/plb_complex/plb_master0,device_type=plb_master)<br />

mem_init(addr=00000000,data=00010203)<br />

mem_init(addr=00000004,data=04050607)<br />

mem_init(addr=00000008,data=08090a0b)<br />

mem_init(addr=0000000c,data=0c0d0e0f)<br />

write(addr=00000000,size=0001,be=1111)<br />

send(level=0)<br />

Cycle<br />

SYS_plbClk<br />

Transfer Qualifiers<br />

Mn_request<br />

Mn_priority(0:1)<br />

Mn_busLock<br />

Mn_RNW<br />

Mn_BE(0:3)<br />

Mn_size(0:3)<br />

Mn_type(0:2)<br />

Mn_abort<br />

Mn_A<strong>Bus</strong>(0:31)<br />

PLB_PAValid<br />

Sl_AddrAck<br />

Sl_wait<br />

Write Data <strong>Bus</strong><br />

Mn_wrD<strong>Bus</strong>(0:31)<br />

Sl_wrDAck<br />

Sl_wrComp<br />

Mn_wrBurst<br />

Read Data <strong>Bus</strong>:<br />

Sl_rdD<strong>Bus</strong>(0:31)<br />

Sl_rdWdAddr(0:3)<br />

Sl_rdDAck<br />

Sl_rdComp<br />

Mn_rdBurst<br />

0 1 2 3 4 5 6 7 8 9<br />

valid<br />

0001<br />

000<br />

A0<br />

Next Rd Avalid<br />

Next Rd AddrAck<br />

W0 W1 W2 W3<br />

0000<br />

0000<br />

Next Wr Avalid<br />

Next Wr AddrAck<br />

Figure 15. Four Word Line Write<br />

Version 4.9.2 PLB <strong>Bus</strong> Timing 65