Processor Local Bus Functional Model Toolkit User's Manual

Processor Local Bus Functional Model Toolkit User's Manual

Processor Local Bus Functional Model Toolkit User's Manual

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

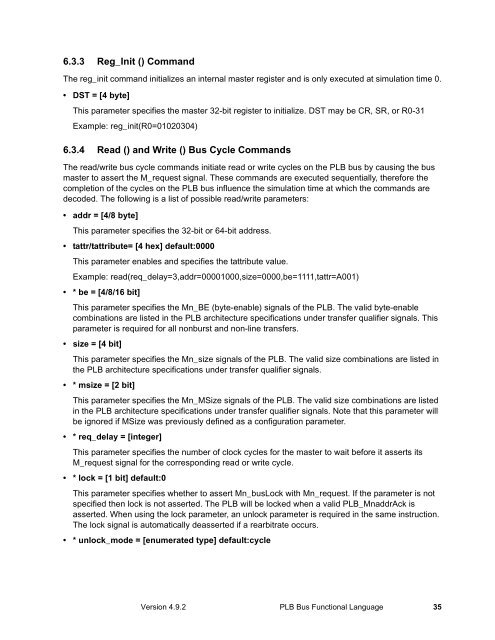

6.3.3 Reg_Init () Command<br />

The reg_init command initializes an internal master register and is only executed at simulation time 0.<br />

• DST = [4 byte]<br />

This parameter specifies the master 32-bit register to initialize. DST may be CR, SR, or R0-31<br />

Example: reg_init(R0=01020304)<br />

6.3.4 Read () and Write () <strong>Bus</strong> Cycle Commands<br />

The read/write bus cycle commands initiate read or write cycles on the PLB bus by causing the bus<br />

master to assert the M_request signal. These commands are executed sequentially, therefore the<br />

completion of the cycles on the PLB bus influence the simulation time at which the commands are<br />

decoded. The following is a list of possible read/write parameters:<br />

• addr = [4/8 byte]<br />

This parameter specifies the 32-bit or 64-bit address.<br />

• tattr/tattribute= [4 hex] default:0000<br />

This parameter enables and specifies the tattribute value.<br />

Example: read(req_delay=3,addr=00001000,size=0000,be=1111,tattr=A001)<br />

• * be = [4/8/16 bit]<br />

This parameter specifies the Mn_BE (byte-enable) signals of the PLB. The valid byte-enable<br />

combinations are listed in the PLB architecture specifications under transfer qualifier signals. This<br />

parameter is required for all nonburst and non-line transfers.<br />

• size = [4 bit]<br />

This parameter specifies the Mn_size signals of the PLB. The valid size combinations are listed in<br />

the PLB architecture specifications under transfer qualifier signals.<br />

• * msize = [2 bit]<br />

This parameter specifies the Mn_MSize signals of the PLB. The valid size combinations are listed<br />

in the PLB architecture specifications under transfer qualifier signals. Note that this parameter will<br />

be ignored if MSize was previously defined as a configuration parameter.<br />

• * req_delay = [integer]<br />

This parameter specifies the number of clock cycles for the master to wait before it asserts its<br />

M_request signal for the corresponding read or write cycle.<br />

• * lock = [1 bit] default:0<br />

This parameter specifies whether to assert Mn_busLock with Mn_request. If the parameter is not<br />

specified then lock is not asserted. The PLB will be locked when a valid PLB_MnaddrAck is<br />

asserted. When using the lock parameter, an unlock parameter is required in the same instruction.<br />

The lock signal is automatically deasserted if a rearbitrate occurs.<br />

• * unlock_mode = [enumerated type] default:cycle<br />

Version 4.9.2 PLB <strong>Bus</strong> <strong>Functional</strong> Language 35