Processor Local Bus Functional Model Toolkit User's Manual

Processor Local Bus Functional Model Toolkit User's Manual

Processor Local Bus Functional Model Toolkit User's Manual

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 7. PLB <strong>Bus</strong> Timing<br />

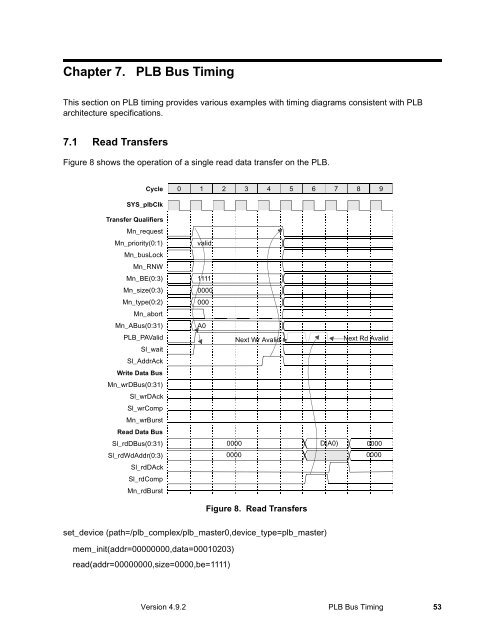

This section on PLB timing provides various examples with timing diagrams consistent with PLB<br />

architecture specifications.<br />

7.1 Read Transfers<br />

Figure 8 shows the operation of a single read data transfer on the PLB.<br />

Cycle<br />

SYS_plbClk<br />

Transfer Qualifiers<br />

Mn_request<br />

Mn_priority(0:1)<br />

Mn_busLock<br />

Mn_RNW<br />

Mn_BE(0:3)<br />

Mn_size(0:3)<br />

Mn_type(0:2)<br />

Mn_abort<br />

Mn_A<strong>Bus</strong>(0:31)<br />

PLB_PAValid<br />

Sl_wait<br />

Sl_AddrAck<br />

Write Data <strong>Bus</strong><br />

Mn_wrD<strong>Bus</strong>(0:31)<br />

Sl_wrDAck<br />

Sl_wrComp<br />

Mn_wrBurst<br />

Read Data <strong>Bus</strong><br />

Sl_rdD<strong>Bus</strong>(0:31)<br />

Sl_rdWdAddr(0:3)<br />

Sl_rdDAck<br />

Sl_rdComp<br />

Mn_rdBurst<br />

set_device (path=/plb_complex/plb_master0,device_type=plb_master)<br />

mem_init(addr=00000000,data=00010203)<br />

read(addr=00000000,size=0000,be=1111)<br />

0 1 2 3 4 5 6 7 8 9<br />

valid<br />

1111<br />

0000<br />

000<br />

A0<br />

Next Wr Avalid<br />

0000 D(A0) 0000<br />

0000<br />

0000<br />

Figure 8. Read Transfers<br />

Next Rd Avalid<br />

Version 4.9.2 PLB <strong>Bus</strong> Timing 53