Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Wouldn’t it be nice to have complex<br />

cores already created and optimized for<br />

<strong>Xilinx</strong> FPGAs? You will use <strong>the</strong> <strong>Xilinx</strong><br />

Architecture Wizard to optimize cores for<br />

instantiation.<br />

You will learn to:<br />

• Use <strong>Xilinx</strong> ISE Project Navigator to<br />

implement an FPGA design<br />

• Read suitable reports to determine<br />

whe<strong>the</strong>r design goals were met<br />

• Assign pin locations with PACE to<br />

enhance performance<br />

• Configure a clocking scheme with <strong>the</strong><br />

Architecture Wizard software<br />

• Use <strong>the</strong> Constraints Editor to create<br />

global timing constraints, which drive<br />

performance<br />

• Specify software options that can boost<br />

performance<br />

• Use synchronous design techniques<br />

to create reliable designs and improve<br />

performance<br />

The Fundamentals of FPGA <strong>Design</strong><br />

course provides <strong>the</strong> necessary foundation to<br />

begin using <strong>Xilinx</strong> FPGAs, create reliable<br />

designs, improve area, and increase performance.<br />

The prerequisites for this course<br />

are basic logic/digital design knowledge<br />

and basic VHDL or Verilog knowledge.<br />

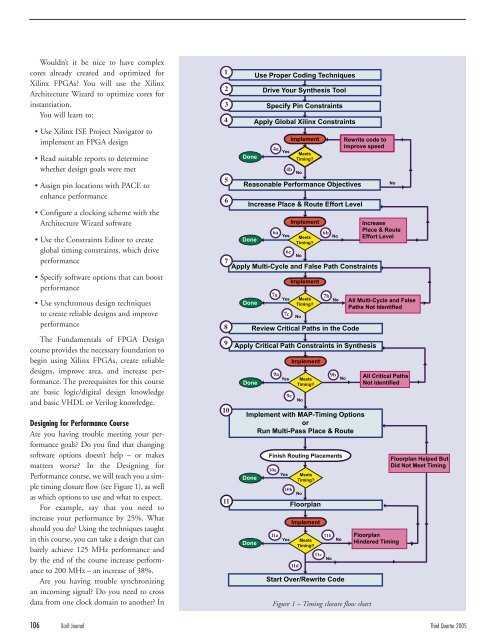

<strong>Design</strong>ing for Performance Course<br />

Are you having trouble meeting your performance<br />

goals? Do you find that changing<br />

software options doesn’t help – or makes<br />

matters worse? In <strong>the</strong> <strong>Design</strong>ing for<br />

Performance course, we will teach you a simple<br />

timing closure flow (see Figure 1), as well<br />

as which options to use and what to expect.<br />

For example, say that you need to<br />

increase your performance by 25%. What<br />

should you do? Using <strong>the</strong> techniques taught<br />

in this course, you can take a design that can<br />

barely achieve 125 MHz performance and<br />

by <strong>the</strong> end of <strong>the</strong> course increase performance<br />

to 200 MHz – an increase of 38%.<br />

Are you having trouble synchronizing<br />

an incoming signal? Do you need to cross<br />

data from one clock domain to ano<strong>the</strong>r? In<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

Done<br />

Use Proper Coding Techniques<br />

Drive Your Syn<strong>the</strong>sis Tool<br />

Apply Global <strong>Xilinx</strong> Constraints<br />

Implement<br />

Increase Place & Route Effort Level<br />

Done<br />

6c<br />

No<br />

7<br />

Apply Multi-Cycle and False Path Constraints<br />

8<br />

9<br />

10<br />

11<br />

Done<br />

Specify Pin Constraints<br />

106 Xcell Journal Third Quarter 2005<br />

4a<br />

Yes<br />

6a<br />

Yes<br />

Yes<br />

Meets<br />

Timing?<br />

No<br />

Reasonable Performance Objectives<br />

Implement<br />

Meets<br />

Timing?<br />

Implement<br />

Meets<br />

Timing?<br />

No<br />

No<br />

6b<br />

No<br />

7b<br />

No<br />

Review Critical Paths in <strong>the</strong> Code<br />

Rewrite code to<br />

improve speed<br />

Apply Critical Path Constraints in Syn<strong>the</strong>sis<br />

Done<br />

Implement<br />

Meets<br />

Timing?<br />

Implement with MAP-Timing Options<br />

or<br />

Run Multi-Pass Place & Route<br />

Done<br />

Done<br />

7a<br />

9a<br />

Yes<br />

Finish Routing Placements<br />

10a<br />

Yes<br />

4b<br />

7c<br />

9c<br />

10b<br />

No<br />

Meets<br />

Timing?<br />

No<br />

Floorplan<br />

Implement<br />

11a<br />

Yes Meets<br />

Timing?<br />

11b<br />

11d<br />

11c<br />

No<br />

9b<br />

No<br />

No<br />

Start Over/Rewrite Code<br />

Figure 1 – Timing closure flow chart<br />

No<br />

Increase<br />

Place & Route<br />

Effort Level<br />

All Multi-Cycle and False<br />

Paths Not Identified<br />

All Critical Paths<br />

Not Identified<br />

Floorplan<br />

Hindered Timing<br />

Floorplan Helped But<br />

Did Not Meet Timing