Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

SYSTEM PERFORMANCE<br />

A(47:0)<br />

CLK<br />

Mapping Beyond Multipliers<br />

Precision Syn<strong>the</strong>sis automatically infers<br />

and maps all multiplier and arithmetic<br />

operators into DSP48 where possible. In<br />

DSP designs, however, critical data paths<br />

are not necessarily always lying on multipliers.<br />

Adders, subtractors, counters, and<br />

o<strong>the</strong>r operators could also be <strong>the</strong> source of<br />

<strong>the</strong> critical timing path. To help deal with<br />

<strong>the</strong>se situations, Precision Syn<strong>the</strong>sis lets<br />

you control each arithmetic operator by<br />

D<br />

Q<br />

+ D Q<br />

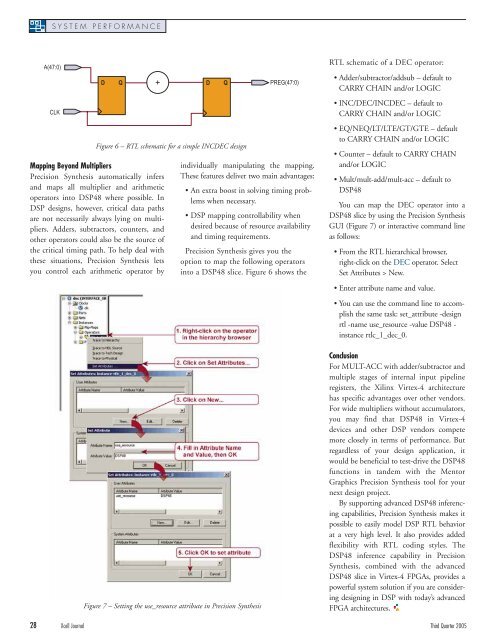

Figure 6 – RTL schematic for a simple INCDEC design<br />

individually manipulating <strong>the</strong> mapping.<br />

These features deliver two main advantages:<br />

• An extra boost in solving timing problems<br />

when necessary.<br />

• DSP mapping controllability when<br />

desired because of resource availability<br />

and timing requirements.<br />

Precision Syn<strong>the</strong>sis gives you <strong>the</strong><br />

option to map <strong>the</strong> following operators<br />

into a DSP48 slice. Figure 6 shows <strong>the</strong><br />

Figure 7 – Setting <strong>the</strong> use_resource attribute in Precision Syn<strong>the</strong>sis<br />

PREG(47:0)<br />

RTL schematic of a DEC operator:<br />

• Adder/subtractor/addsub – default to<br />

CARRY CHAIN and/or LOGIC<br />

• INC/DEC/INCDEC – default to<br />

CARRY CHAIN and/or LOGIC<br />

• EQ/NEQ/LT/LTE/GT/GTE – default<br />

to CARRY CHAIN and/or LOGIC<br />

• Counter – default to CARRY CHAIN<br />

and/or LOGIC<br />

• Mult/mult-add/mult-acc – default to<br />

DSP48<br />

You can map <strong>the</strong> DEC operator into a<br />

DSP48 slice by using <strong>the</strong> Precision Syn<strong>the</strong>sis<br />

GUI (Figure 7) or interactive command line<br />

as follows:<br />

• From <strong>the</strong> RTL hierarchical browser,<br />

right-click on <strong>the</strong> DEC operator. Select<br />

Set Attributes > New.<br />

• Enter attribute name and value.<br />

• You can use <strong>the</strong> command line to accomplish<br />

<strong>the</strong> same task: set_attribute -design<br />

rtl -name use_resource -value DSP48 -<br />

instance rtlc_1_dec_0.<br />

Conclusion<br />

For MULT-ACC with adder/subtractor and<br />

multiple stages of internal input pipeline<br />

registers, <strong>the</strong> <strong>Xilinx</strong> Virtex-4 architecture<br />

has specific advantages over o<strong>the</strong>r vendors.<br />

For wide multipliers without accumulators,<br />

you may find that DSP48 in Virtex-4<br />

devices and o<strong>the</strong>r DSP vendors compete<br />

more closely in terms of performance. But<br />

regardless of your design application, it<br />

would be beneficial to test-drive <strong>the</strong> DSP48<br />

functions in tandem with <strong>the</strong> Mentor<br />

Graphics Precision Syn<strong>the</strong>sis tool for your<br />

next design project.<br />

By supporting advanced DSP48 inferencing<br />

capabilities, Precision Syn<strong>the</strong>sis makes it<br />

possible to easily model DSP RTL behavior<br />

at a very high level. It also provides added<br />

flexibility with RTL coding styles. The<br />

DSP48 inference capability in Precision<br />

Syn<strong>the</strong>sis, combined with <strong>the</strong> advanced<br />

DSP48 slice in Virtex-4 FPGAs, provides a<br />

powerful system solution if you are considering<br />

designing in DSP with today’s advanced<br />

FPGA architectures.<br />

28 Xcell Journal Third Quarter 2005