Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

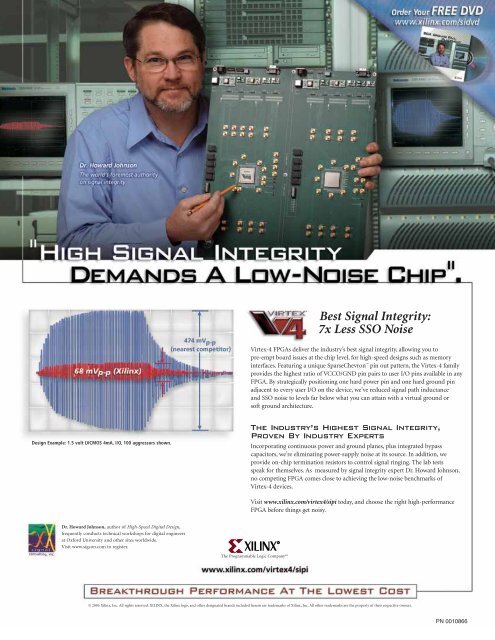

<strong>Design</strong> Example: 1.5 volt LVCMOS 4mA, I/O, 100 aggressors shown.<br />

Dr. Howard Johnson, author of High-Speed Digital <strong>Design</strong>,<br />

frequently conducts technical workshops for digital engineers<br />

at Oxford University and o<strong>the</strong>r sites worldwide.<br />

Visit www.sigcon.com to register.<br />

Best Signal Integrity:<br />

7x Less SSO Noise<br />

Virtex-4 FPGAs deliver <strong>the</strong> industry’s best signal integrity, allowing you to<br />

pre-empt board issues at <strong>the</strong> chip level, for high-speed designs such as memory<br />

interfaces. Featuring a unique SparseChevron pin out pattern, <strong>the</strong> Virtex-4 family<br />

provides <strong>the</strong> highest ratio of VCCO/GND pin pairs to user I/O pins available in any<br />

FPGA. By strategically positioning one hard power pin and one hard ground pin<br />

adjacent to every user I/O on <strong>the</strong> device, we’ve reduced signal path inductance<br />

and SSO noise to levels far below what you can attain with a virtual ground or<br />

soft ground architecture.<br />

The Industry’s Highest Signal Integrity,<br />

Proven By Industry Experts<br />

Incorporating continuous power and ground planes, plus integrated bypass<br />

capacitors, we’re eliminating power-supply noise at its source. In addition, we<br />

provide on-chip termination resistors to control signal ringing. The lab tests<br />

speak for <strong>the</strong>mselves. As measured by signal integrity expert Dr. Howard Johnson,<br />

no competing FPGA comes close to achieving <strong>the</strong> low-noise benchmarks of<br />

Virtex-4 devices.<br />

Visit www.xilinx.com/virtex4/sipi today, and choose <strong>the</strong> right high-performance<br />

FPGA before things get noisy.<br />

The Programmable Logic Company SM<br />

© 2005 <strong>Xilinx</strong>, Inc. All rights reserved. XILINX, <strong>the</strong> <strong>Xilinx</strong> logo, and o<strong>the</strong>r designated brands included herein are trademarks of <strong>Xilinx</strong>, Inc. All o<strong>the</strong>r trademarks are <strong>the</strong> property of <strong>the</strong>ir respective owners.<br />

PN 0010866