Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

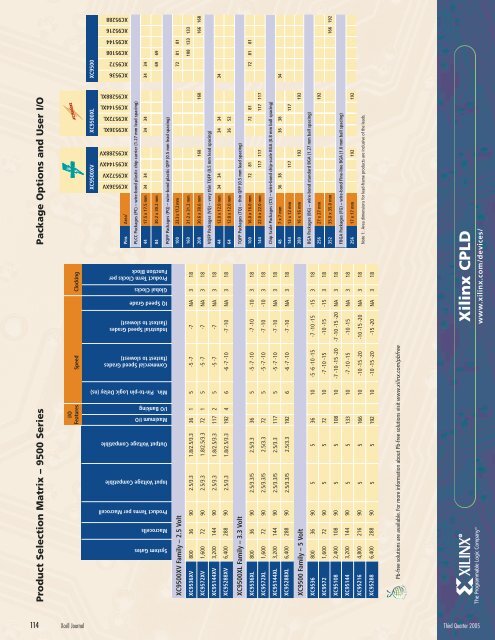

Product Selection Matrix – 9500 Series Package Options and User I/O<br />

I/O<br />

Features Speed Clocking<br />

XC9500<br />

XC9500XL<br />

XC9500XV<br />

XC95288<br />

XC95216<br />

XC95144<br />

XC95108<br />

XC9572<br />

XC9536<br />

XC95288XL<br />

XC95144XL<br />

XC9572XL<br />

XC9536XL<br />

XC95288XV<br />

XC95144XV<br />

XC9572XV<br />

XC9536XV<br />

Area 1<br />

Pins<br />

PLCC Packages (PC) – wire-bond plastic chip carrier (1.27 mm lead spacing)<br />

34 34<br />

34 34<br />

34 34<br />

17.5 x 17.5 mm<br />

44<br />

84 30.2 x 30.2 mm<br />

69 69<br />

Min. Pin-to-pin Logic Delay (ns)<br />

PQFP Packages (PQ) – wire-bond plastic QFP (0.5 mm lead spacing)<br />

Product Term Clocks per<br />

Function Block<br />

Global Clocks<br />

IQ Speed Grade<br />

Industrial Speed Grades<br />

(fastest to slowest)<br />

Commercial Speed Grades<br />

(fastest to slowest)<br />

I/O Banking<br />

Maximum I/O<br />

Output Voltage Compatible<br />

Input Voltage Compatible<br />

Product Terms per Macrocell<br />

Macrocells<br />

System Gates<br />

72 81 81<br />

23.3 x 17.2 mm<br />

100<br />

160 31.2 x 31.2 mm<br />

108 133 133<br />

36 1 5 -5 -7 -7 NA 3 18<br />

1.8/2.5/3.3<br />

2.5/3.3<br />

208 30.6 x 30.6 mm<br />

168 168<br />

166 168<br />

72 1 5 -5 -7 -7 NA 3 18<br />

1.8/2.5/3.3<br />

2.5/3.3<br />

VQFP Packages (VQ) – very thin TQFP (0.5 mm lead spacing)<br />

44 12.0 x 12.0 mm 34 34 34 34<br />

34<br />

64 12.0 x 12.0 mm<br />

36 52<br />

117 2 5 -5 -7 -7 NA 3 18<br />

192 4 6 -6 -7 -10 -7 -10 NA 3 18<br />

1.8/2.5/3.3<br />

2.5/3.3<br />

1.8/2.5/3.3<br />

2.5/3.3<br />

XC9500XV Family – 2.5 Volt<br />

XC9536XV 800 36 90<br />

XC9572XV 1,600 72 90<br />

XC95144XV 3,200 144 90<br />

XC95288XV 6,400 288 90<br />

81 81<br />

72<br />

TQFP Packages (TQ) – thin QFP (0.5 mm lead spacing)<br />

100 16.0 x 16.0 mm 72 81 72 81<br />

XC9500XL Family – 3.3 Volt<br />

36 5 -5 -7 -10 -7 -10 -10 3 18<br />

2.5/3.3<br />

2.5/3.3/5<br />

90<br />

XC9536XL 800 36<br />

114 Xcell Journal Third Quarter 2005<br />

117 117 117 117<br />

22.0 x 22.0 mm<br />

144<br />

72 5 -5 -7 -10 -7 -10 -10 3 18<br />

2.5/3.3<br />

2.5/3.3/5<br />

90<br />

XC9572XL 1,600 72<br />

Chip Scale Packages (CS) – wire-bond chip-scale BGA (0.8 mm ball spacing)<br />

90<br />

XC95144XL 3,200 144<br />

34<br />

36 38<br />

36 38<br />

7 x 7 mm<br />

48<br />

117 5 -5 -7 -10 -7 -10 NA 3 18<br />

192 6 -6 -7 -10 -7 -10 NA 3 18<br />

2.5/3.3<br />

2.5/3.3/5<br />

117 117<br />

12 x 12 mm<br />

144<br />

2.5/3.3<br />

2.5/3.3/5<br />

90<br />

XC95288XL 6,400 288<br />

192 192<br />

16 x 16 mm<br />

280<br />

XC9500 Family – 5 Volt<br />

BGA Packages (BG) – wire-bond standard BGA (1.27 mm ball spacing)<br />

36 10 -5 -6 -10 -15 -7 -10 -15 -15 3 18<br />

90<br />

XC9536 800 36<br />

192<br />

27 x 27 mm<br />

256<br />

72 10 -7 -10 -15 -10 -15 -15 3 18<br />

90<br />

XC9572 1,600 72<br />

352 35.0 x 35.0 mm<br />

166 192<br />

90<br />

XC95108 2,400 108<br />

FBGA Packages (FG) – wire-bond Fine-line BGA (1.0 mm ball spacing)<br />

108 10 -7 -10 -15 -20 -7 -10 -15 -20 NA 3 18<br />

133 10 -7 -10 -15 -10 -15 NA 3 18<br />

5<br />

5<br />

5<br />

5<br />

5<br />

5<br />

5<br />

5<br />

90<br />

XC95144 3,200 144<br />

192 192<br />

17 x 17 mm<br />

256<br />

Note 1: Area dimensions for lead-frame products are inclusive of <strong>the</strong> leads.<br />

XC95216 4,800 216 90 5 5 166 10 -10 -15 -20 -10 -15 -20 NA 3 18<br />

288 90 5 5 192 10 -10 -15 -20 -15 -20 NA 3 18<br />

XC95288 6,400<br />

Pb-free solutions are available. For more information about Pb-free solutions visit www.xilinx.com/pbfree<br />

<strong>Xilinx</strong> CPLD<br />

www.xilinx.com/devices/