Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

Design Challenges: Avoiding the Pitfalls, winning the game - Xilinx

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Xilinx</strong> CPLD<br />

www.xilinx.com/devices/<br />

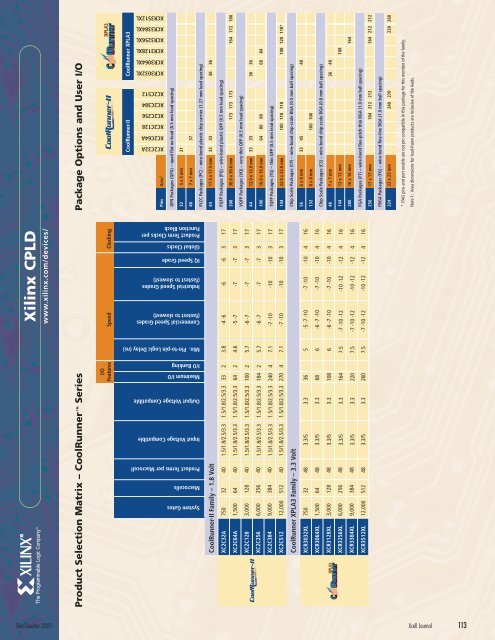

Product Selection Matrix – CoolRunner Series Package Options and User I/O<br />

I/O<br />

Features Speed Clocking<br />

CoolRunner XPLA3<br />

CoolRunner-II<br />

XC2C512 XCR3512XL<br />

XCR3384XL<br />

XCR3256XL<br />

XCR3128XL<br />

XCR3064XL<br />

XCR3032XL<br />

XC2C512<br />

XC2C384<br />

XC2C256<br />

XC2C128<br />

XC2C64A<br />

XC2C32A<br />

Area 1<br />

Pins<br />

QFN Packages (QFG) – quad flat no-lead (0.5 mm lead spacing)<br />

32 5 x 5 mm 21<br />

48 7 x 7 mm<br />

37<br />

PLCC Packages (PC) – wire-bond plastic chip carrier (1.27 mm lead spacing)<br />

44 17.5 x 17.5 mm 33 33<br />

36 36<br />

Product Term Clocks per<br />

Function Block<br />

Global Clocks<br />

IQ Speed Grade<br />

Industrial Speed Grades<br />

(fastest to slowest)<br />

Commercial Speed Grades<br />

(fastest to slowest)<br />

Min. Pin-to-pin Logic Delay (ns)<br />

I/O Banking<br />

Maximum I/O<br />

Output Voltage Compatible<br />

Input Voltage Compatible<br />

Product Terms per Macrocell<br />

Macrocells<br />

System Gates<br />

CoolRunner-II Family – 1.8 Volt<br />

PQFP Packages (PQ) – wire-bond plastic QFP (0.5 mm lead spacing)<br />

17<br />

3<br />

-6<br />

-4 -6 -6<br />

2 3.8<br />

1.5/1.8/2.5/3.3 33<br />

1.5/1.8/2.5/3.3<br />

40<br />

XC2C32A 750 32<br />

173 173 173 164 172 180<br />

30.6 x 30.6 mm<br />

208<br />

1.5/1.8/2.5/3.3 1.5/1.8/2.5/3.3 64 2 4.6 -5 -7 -7 -7 3 17<br />

40<br />

XC2C64A 1,500 64<br />

VQFP Packages (VQ) – very thin QFP (0.5 mm lead spacing)<br />

1.5/1.8/2.5/3.3 1.5/1.8/2.5/3.3 100 2 5.7 -6 -7 -7 -7 3 17<br />

3.3 36 5 -5 -7 -10 -7 -10 -10 4 16<br />

3.3 68 6 -6 -7 -10 -7 -10 -10 4 16<br />

3.3 108 6 -6 -7 -10 -7 -10 -10 4 16<br />

3.3 164 7.5 -7 -10 -12 -10 -12 -12 4 16<br />

3.3 220 7.5 -7 -10 -12 -10 -12 -12 4 16<br />

3.3 260 7.5 -7 -10 -12 -10 -12 -12 4 16<br />

Third Quarter 2005 Xcell Journal 113<br />

33 33 36 36<br />

40<br />

XC2C128 3,000 128<br />

12.0 x 12.0 mm<br />

44<br />

68 84<br />

64 80 80<br />

16.0 x 16.0 mm<br />

100<br />

1.5/1.8/2.5/3.3 1.5/1.8/2.5/3.3 184 2 5.7 -6 -7 -7 -7 3 17<br />

40<br />

XC2C256 6,000 256<br />

TQFP Packages (TQ) – thin QFP (0.5 mm lead spacing)<br />

1.5/1.8/2.5/3.3 1.5/1.8/2.5/3.3 240 4 7.1 -7 -10 -10 -10 3 17<br />

1.5/1.8/2.5/3.3 1.5/1.8/2.5/3.3 270 4 7.1 -7 -10 -10 -10 3 17<br />

40<br />

XC2C384 9,000 384<br />

118*<br />

108 120<br />

100 118 118<br />

22.0 x 22.0 mm<br />

144<br />

40<br />

XC2C512 12,000 512<br />

Chip Scale Packages (CP) – wire-bond chip-scale BGA (0.5 mm ball spacing)<br />

56 6 x 6 mm 33 45<br />

48<br />

CoolRunner XPLA3 Family – 3.3 Volt<br />

3.3/5<br />

48<br />

XCR3032XL 750 32<br />

132 8 x 8 mm<br />

100 106<br />

Chip Scale Packages (CS) – wire-bond chip-scale BGA (0.8 mm ball spacing)<br />

48 7 x 7 mm<br />

36 40<br />

3.3/5<br />

48<br />

XCR3064XL 1,500 64<br />

3.3/5<br />

48<br />

XCR3128XL 3,000 128<br />

108<br />

12 x 12 mm<br />

144<br />

3.3/5<br />

48<br />

XCR3256XL 6,000 256<br />

164<br />

16 x 16 mm<br />

280<br />

3.3/5<br />

48<br />

XCR3384XL 9,000 384<br />

FGA Packages (FT) – wire-bond fine-pitch thin BGA (1.0 mm ball spacing)<br />

3.3/5<br />

48<br />

XCR3512XL 12,000 512<br />

212<br />

164 212<br />

256 17 x 17 mm<br />

184 212 212<br />

FBGA Packages (FG) – wire-bond fine-line BGA (1.0 mm ball spacing)<br />

260<br />

220<br />

324 23 x 23 mm<br />

240 270<br />

* JTAG pins and port enable are not pin compatible in this package for this member of <strong>the</strong> family.<br />

Note 1: Area dimensions for lead-frame products are inclusive of <strong>the</strong> leads.