Top-down digital design flow - Microelectronic Systems Laboratory

Top-down digital design flow - Microelectronic Systems Laboratory

Top-down digital design flow - Microelectronic Systems Laboratory

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

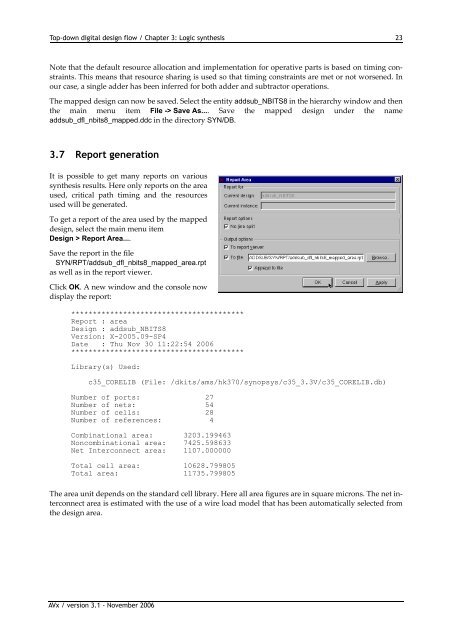

<strong>Top</strong>-<strong>down</strong> <strong>digital</strong> <strong>design</strong> <strong>flow</strong> / Chapter 3: Logic synthesis 23Note that the default resource allocation and implementation for operative parts is based on timing constraints.This means that resource sharing is used so that timing constraints are met or not worsened. Inour case, a single adder has been inferred for both adder and subtractor operations.The mapped <strong>design</strong> can now be saved. Select the entity addsub_NBITS8 in the hierarchy window and thenthe main menu item File -> Save As.... Save the mapped <strong>design</strong> under the nameaddsub_dfl_nbits8_mapped.ddc in the directory SYN/DB.3.7 Report generationIt is possible to get many reports on varioussynthesis results. Here only reports on the areaused, critical path timing and the resourcesused will be generated.To get a report of the area used by the mapped<strong>design</strong>, select the main menu itemDesign > Report Area....Save the report in the fileSYN/RPT/addsub_dfl_nbits8_mapped_area.rptas well as in the report viewer.Click OK. A new window and the console nowdisplay the report:****************************************Report : areaDesign : addsub_NBITS8Version: X-2005.09-SP4Date : Thu Nov 30 11:22:54 2006****************************************Library(s) Used:c35_CORELIB (File: /dkits/ams/hk370/synopsys/c35_3.3V/c35_CORELIB.db)Number of ports: 27Number of nets: 54Number of cells: 28Number of references: 4Combinational area: 3203.199463Noncombinational area: 7425.598633Net Interconnect area: 1107.000000Total cell area: 10628.799805Total area: 11735.799805The area unit depends on the standard cell library. Here all area figures are in square microns. The net interconnectarea is estimated with the use of a wire load model that has been automatically selected fromthe <strong>design</strong> area.AVx / version 3.1 - November 2006